<u>Art Margolis</u> MANUALE DI RIPARAZIONE DEL COMMODORE 64 UNIVERSAL COUNTER UC 503 A FREQ x10 LP1KHz +20 TOTAL PER TEST RESET HOLD M

© Copyright per l'edizione originale: 1985 by TAB BOOKS Inc. © Copyright per l'edizione italiana: Gruppo Editoriale Jackson - Novembre 1987

TRADUZIONE: Studio Professionale

Ing. Marcello G. Falconi

REDATTORE DI COLLANA: Mauro Risani

GRAFICA E IMPAGINAZIONE: Francesca di Fiore

Moreno Confalone

COPERTINA: Emilano Bernasconi FOTOCOMPOSIZIONE: Visualtype - MI

STAMPA: Rotolito Lombarda - MI

Tutti i diritti sono riservati. Stampato in Italia. Nessuna parte di questo libro può essere riprodotta, memorizzata in sistemi di archivio, o trasmessa in qualsiasi forma o mezzo, elettronico, meccanico, fotocopia, registrazione o altri senza la preventiva autorizzazione scritta dell'editore.

## MANUALE DI RIPARAZIONE DEL COMMODORE 64

Art Margolis

GRUPPO EDITORIALE JACKSON Via Rosellini, 12 20124 Milano

### Indice

| Prefazione all'edizione italiana                 | 1  |

|--------------------------------------------------|----|

| Introduzione                                     | 3  |

| Capitolo 1                                       |    |

| Interpretazione dei sintomi                      | 9  |

| Sintomi comuni                                   | 10 |

| Computer che non dà segni di vita                | 10 |

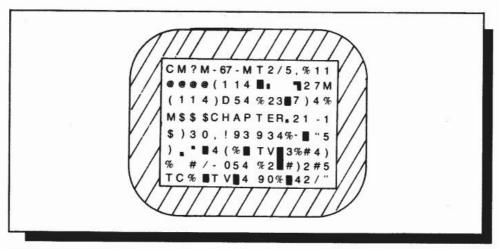

| Visualizzazione di "spazzatura"                  | 11 |

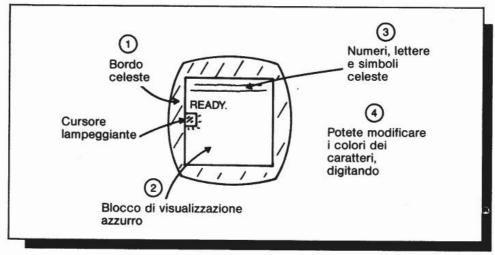

| Visualizzazione del quadro vuoto                 | 13 |

| Assenza di colore                                | 14 |

| Assenza di immagine video; suono corretto        | 14 |

| Assenza di suono                                 | 15 |

| Guasti nei dispositivi esterni                   | 15 |

| Programmazione diagnostica                       | 16 |

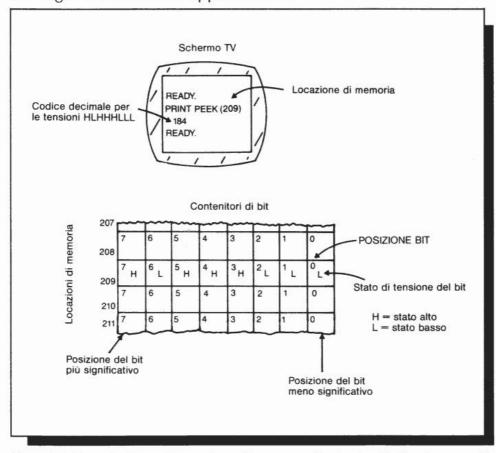

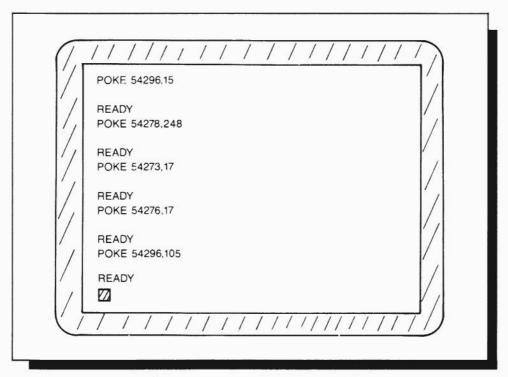

| PEEK e POKE                                      | 16 |

| Programmi diagnostici                            | 18 |

| All'interno del C-64                             | 20 |

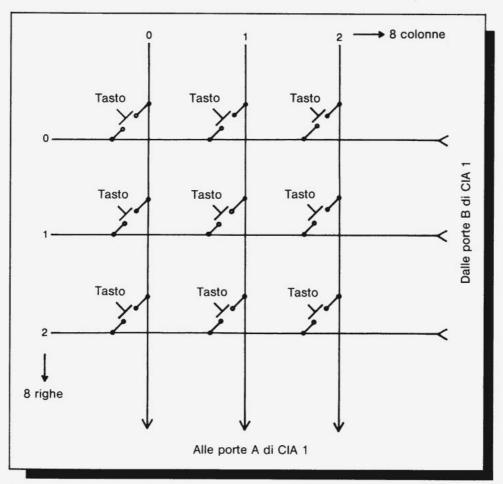

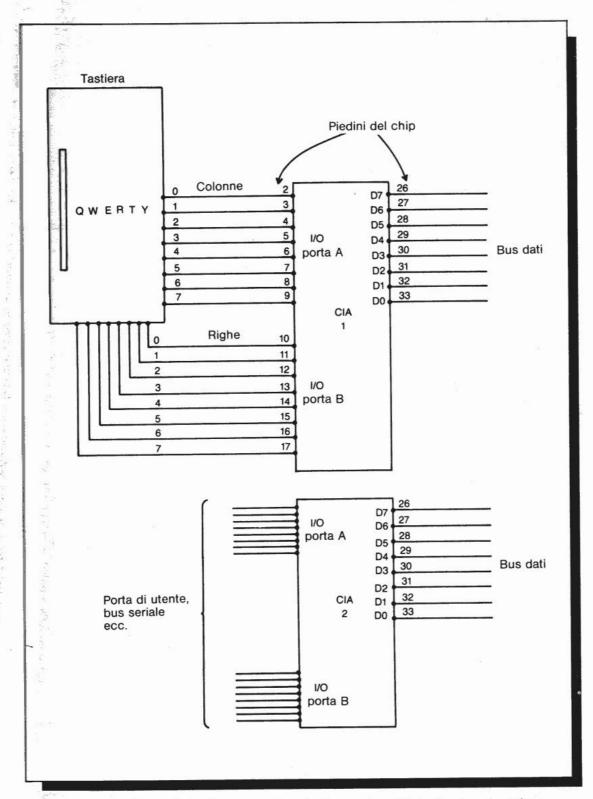

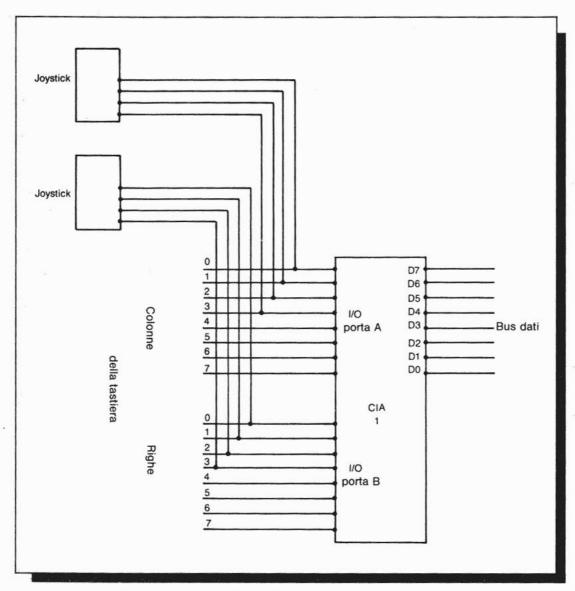

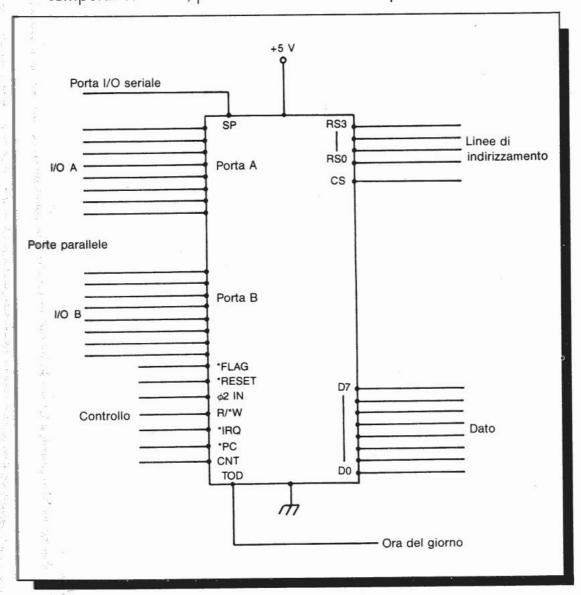

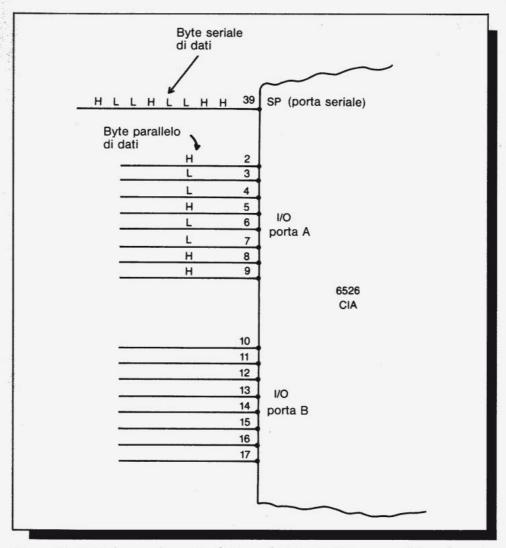

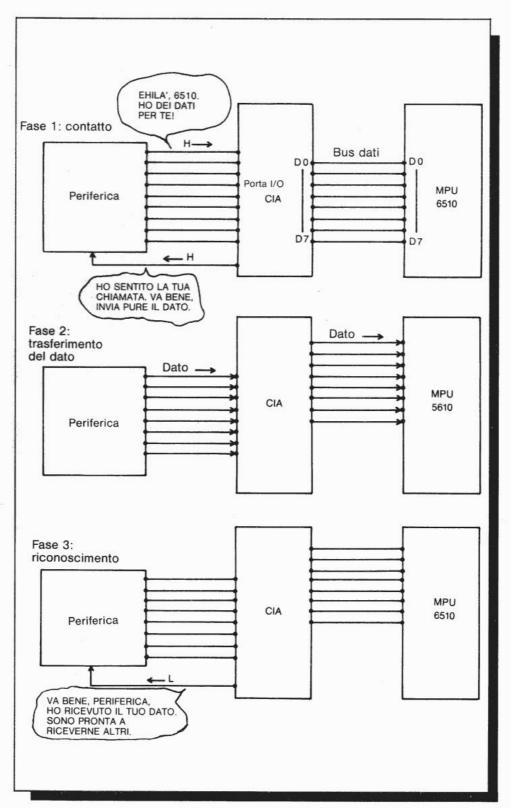

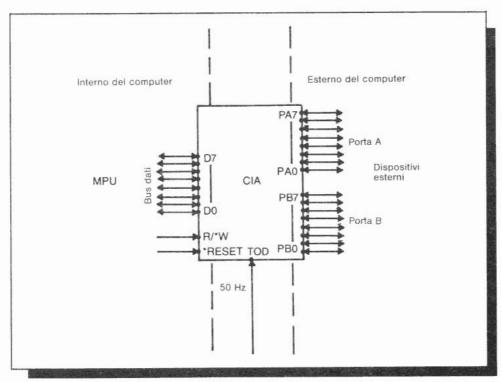

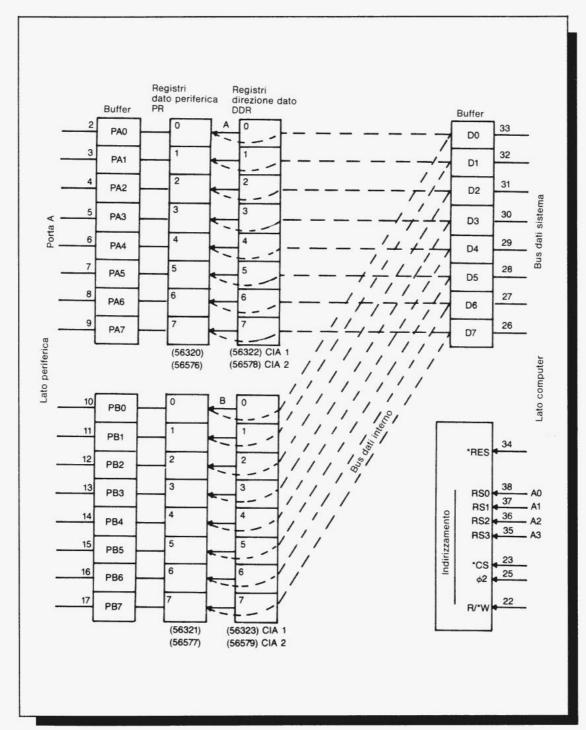

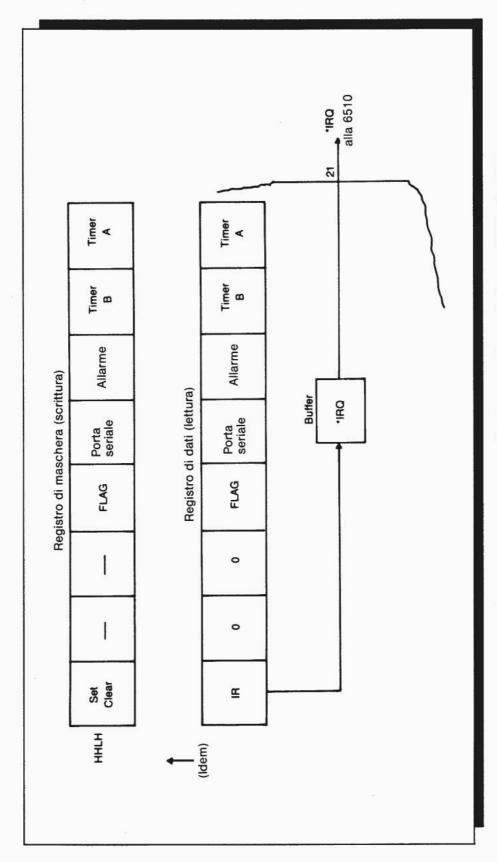

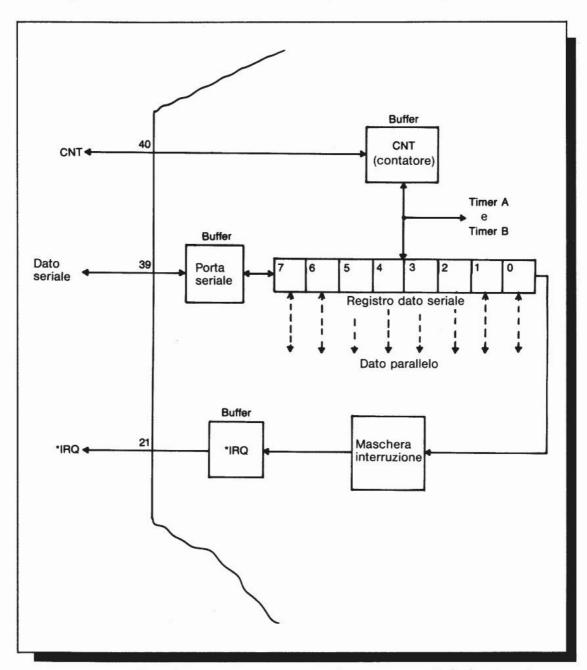

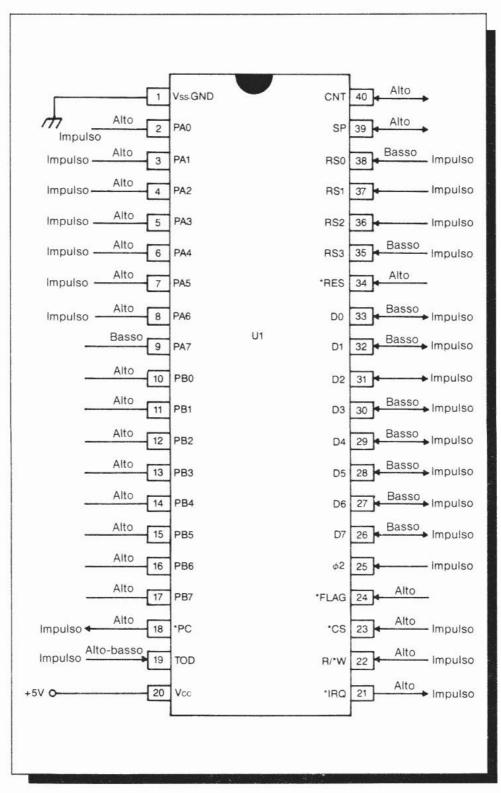

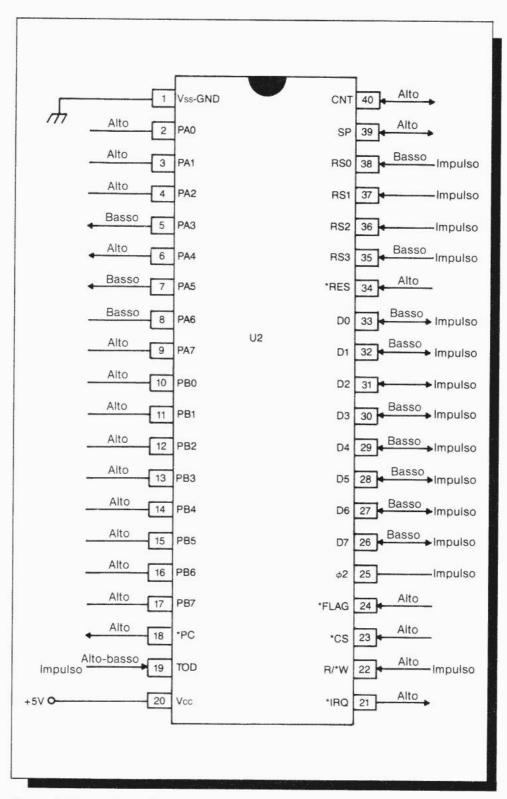

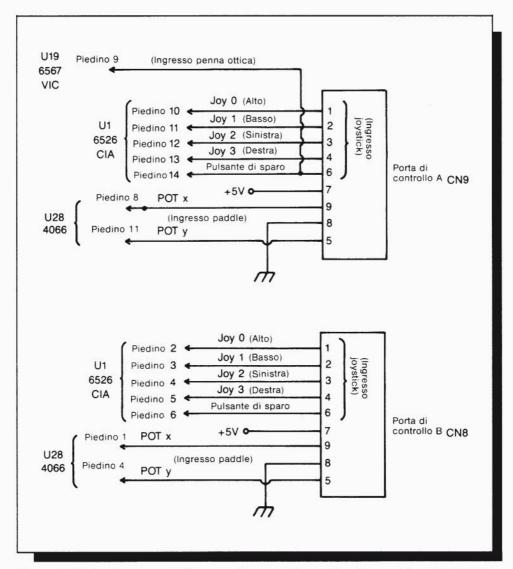

| L'adattatore di interfaccia complessa (CIA)      | 21 |

| Il microprocessore (MPU)                         | 23 |

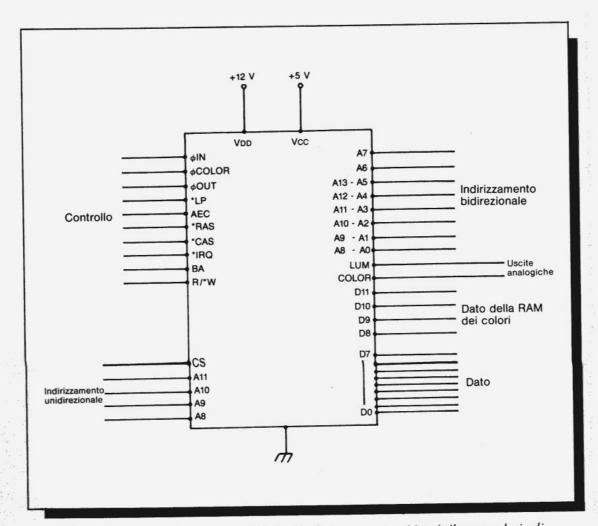

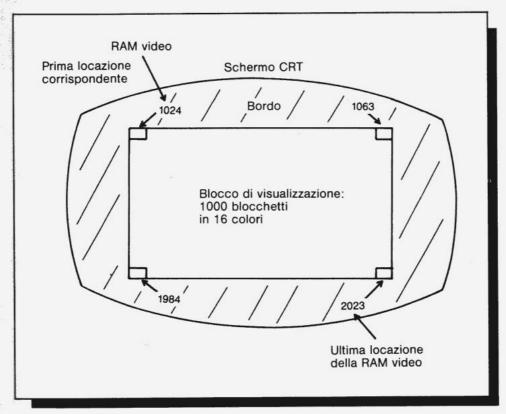

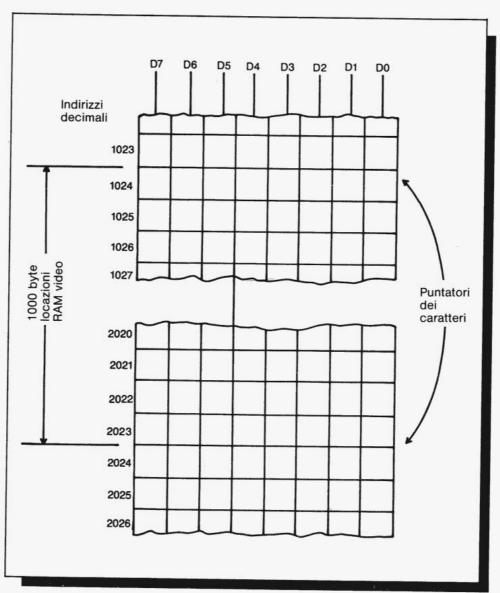

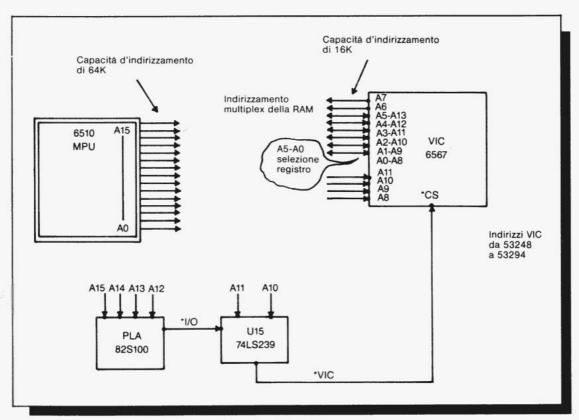

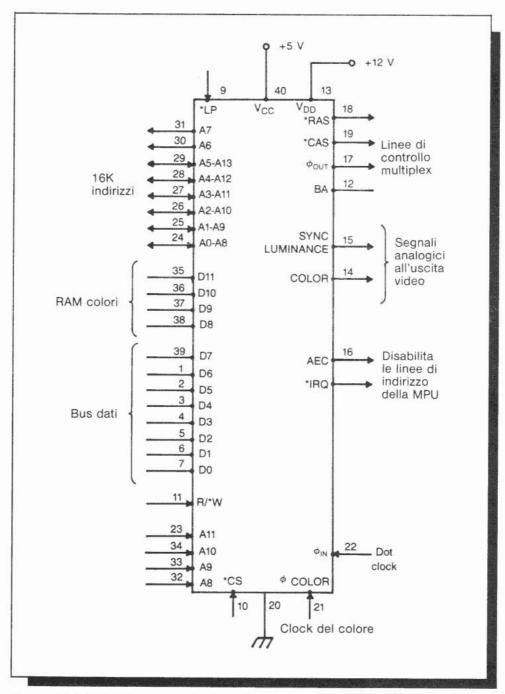

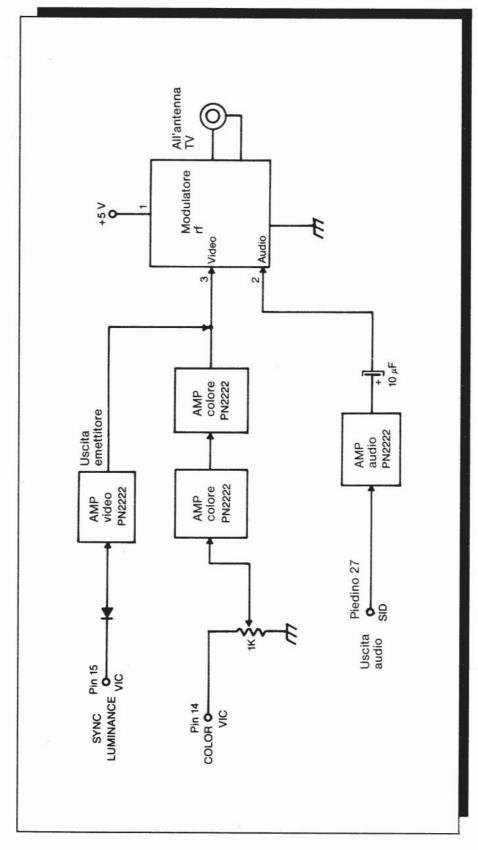

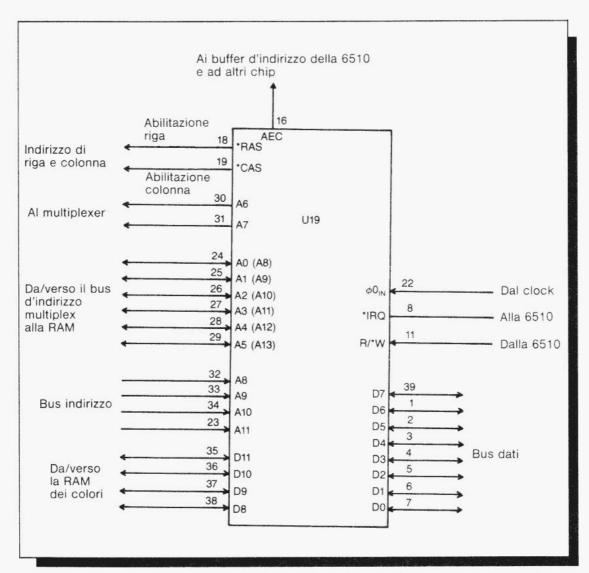

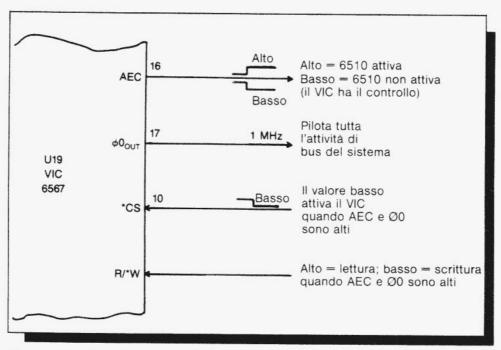

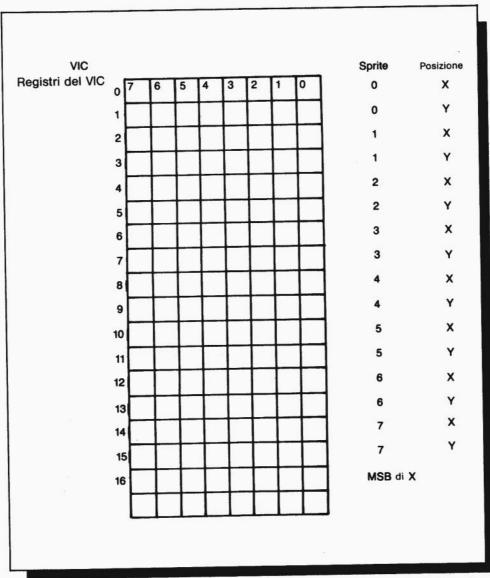

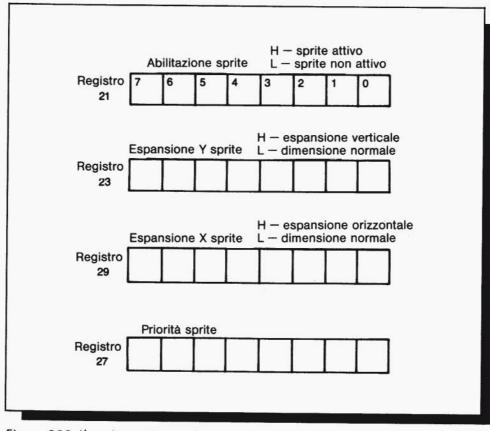

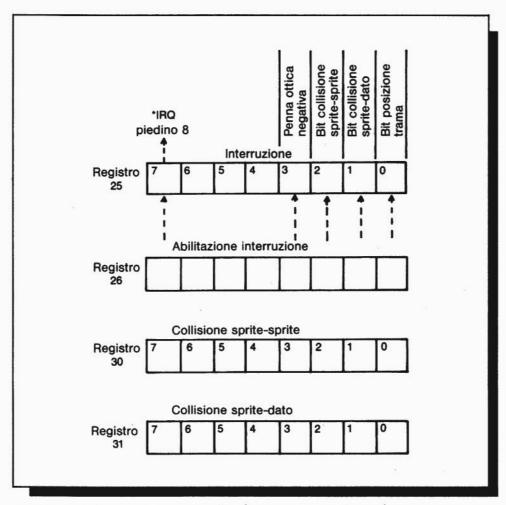

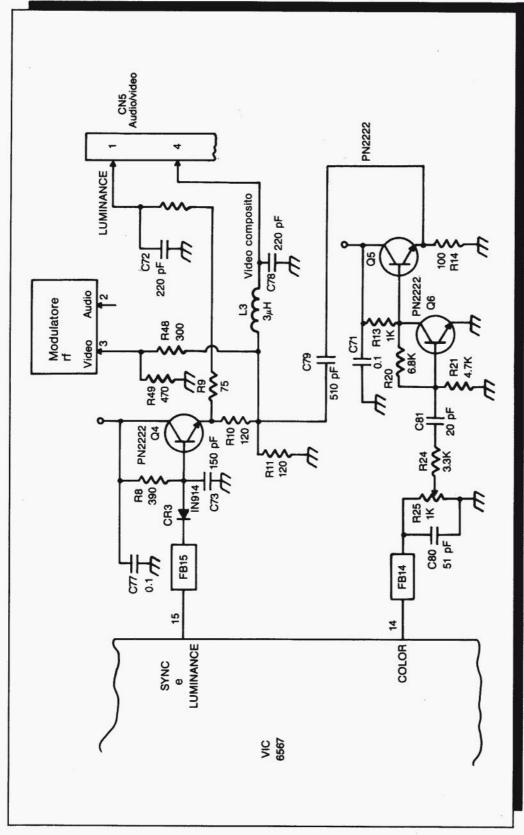

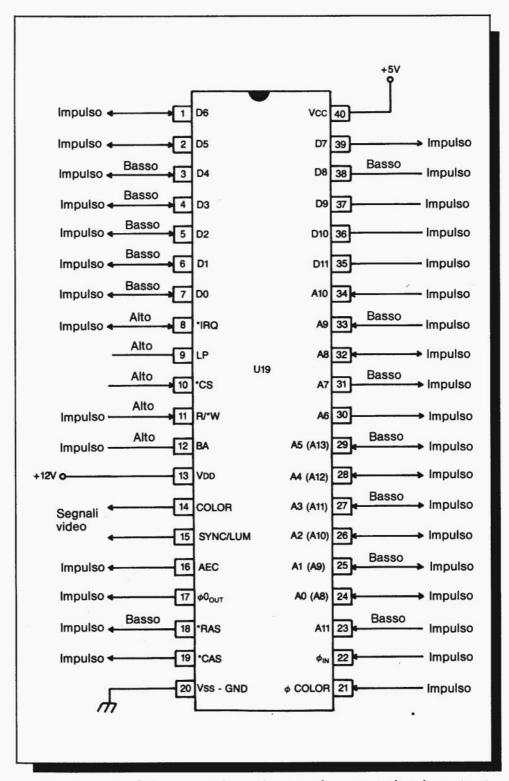

| Il chip di interfaccia video (VIC)               | 26 |

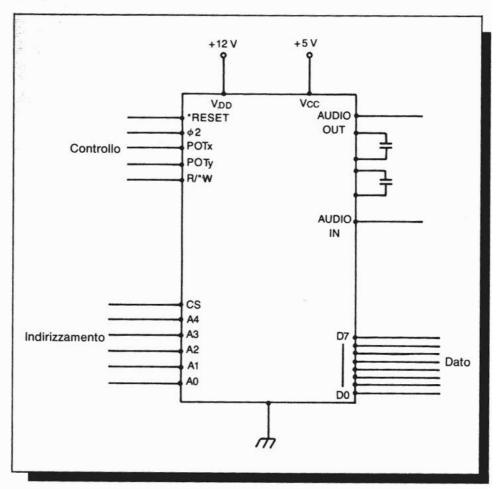

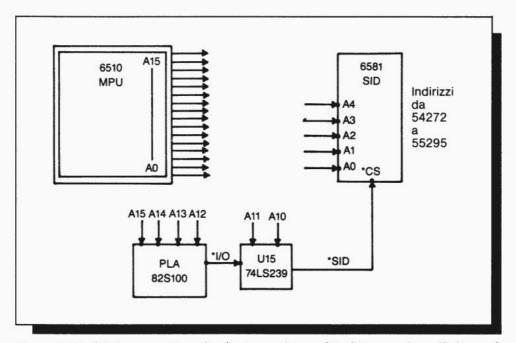

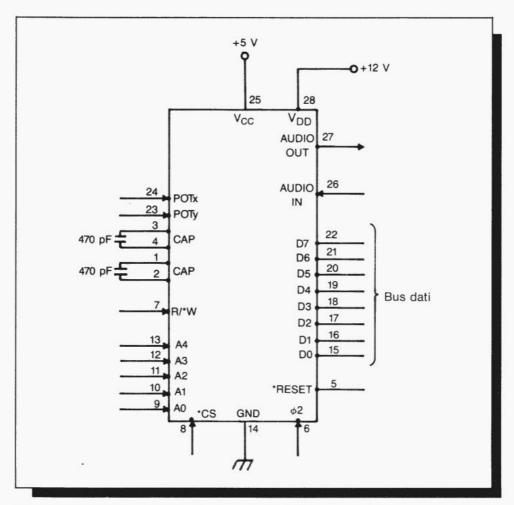

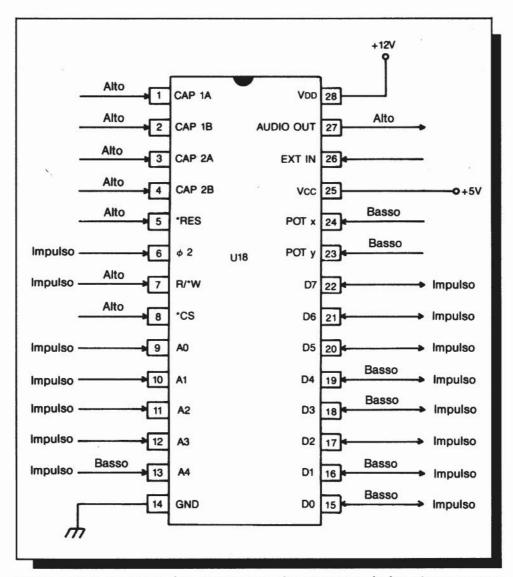

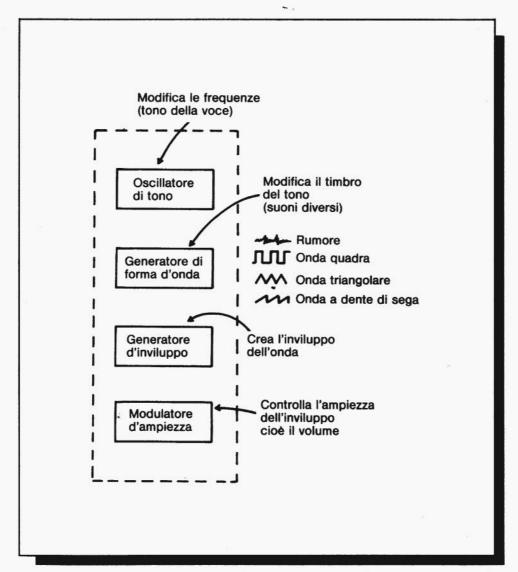

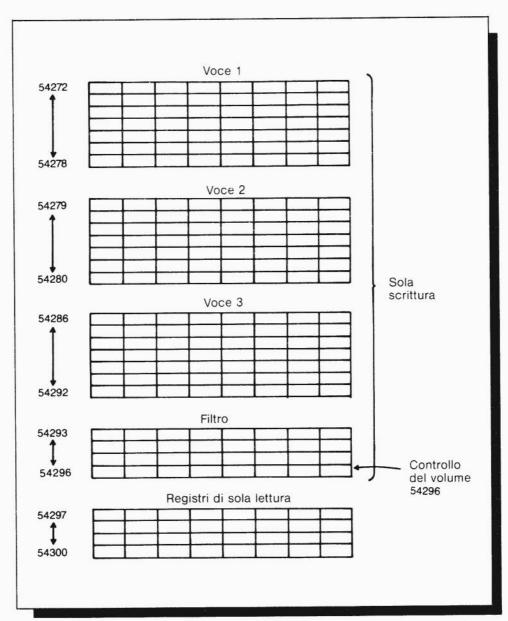

| Il dispositivo di interfaccia per il suono (SID) | 27 |

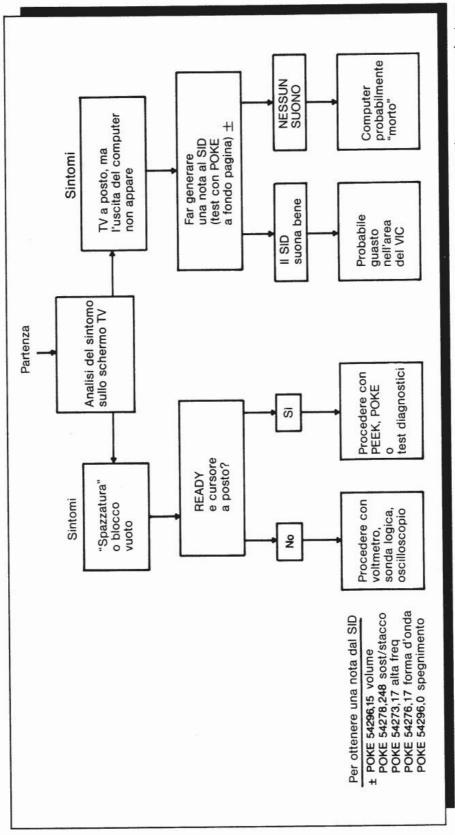

| Diagrammi per la ricerca dei guasti              | 27 |

| Capitolo 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

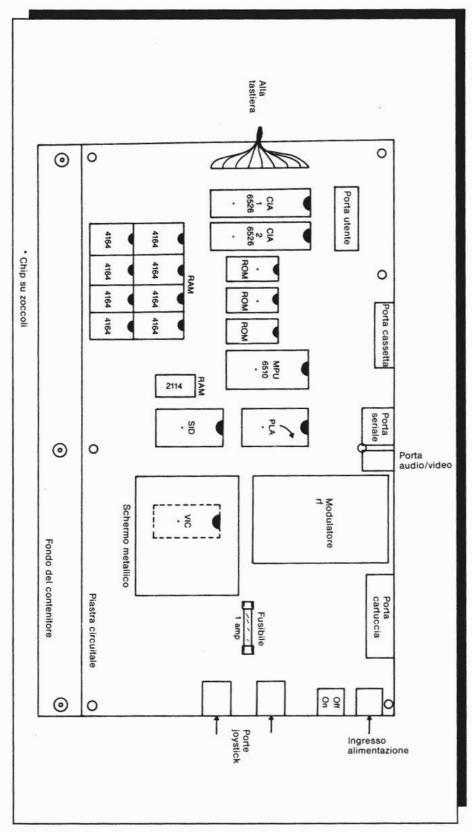

| Smontaggio del computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

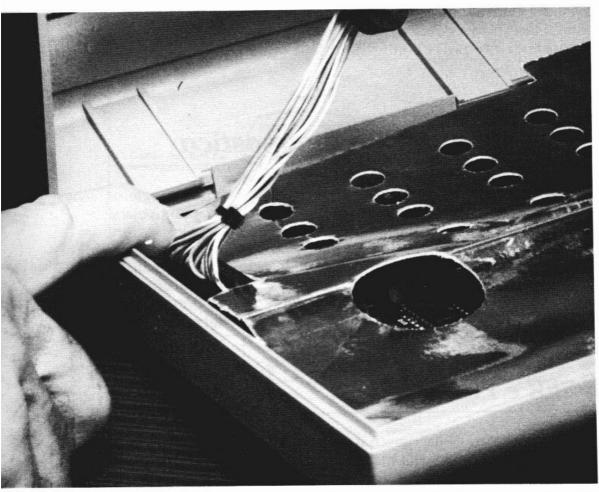

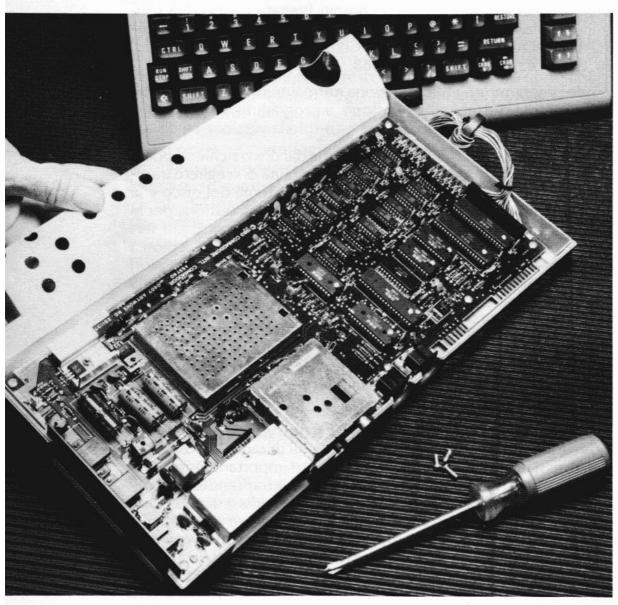

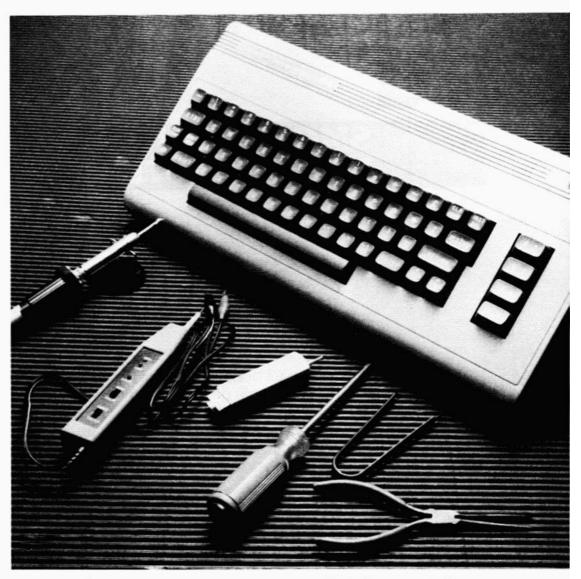

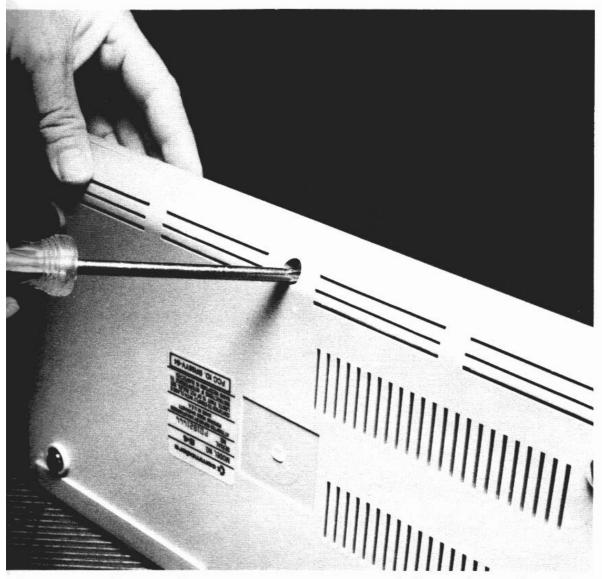

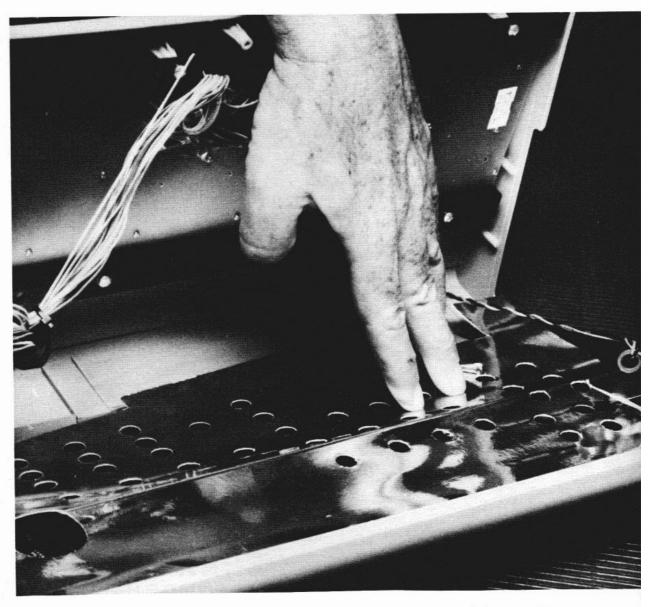

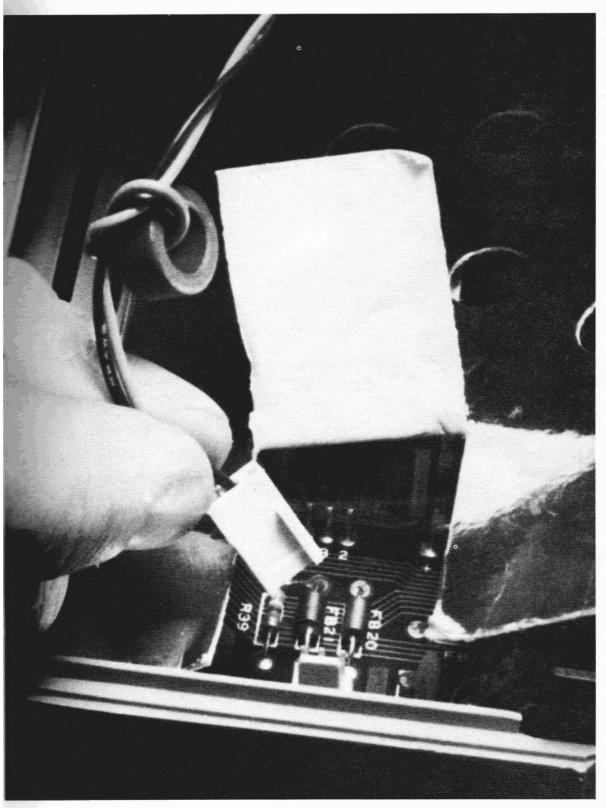

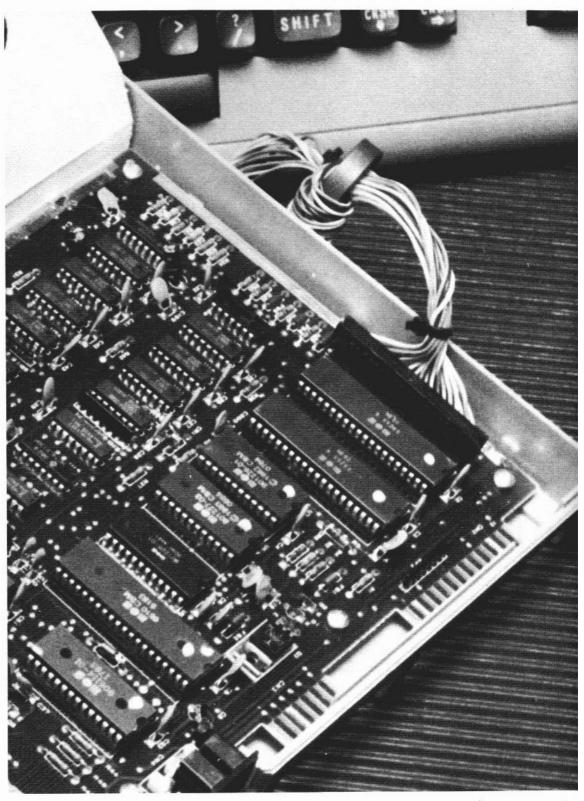

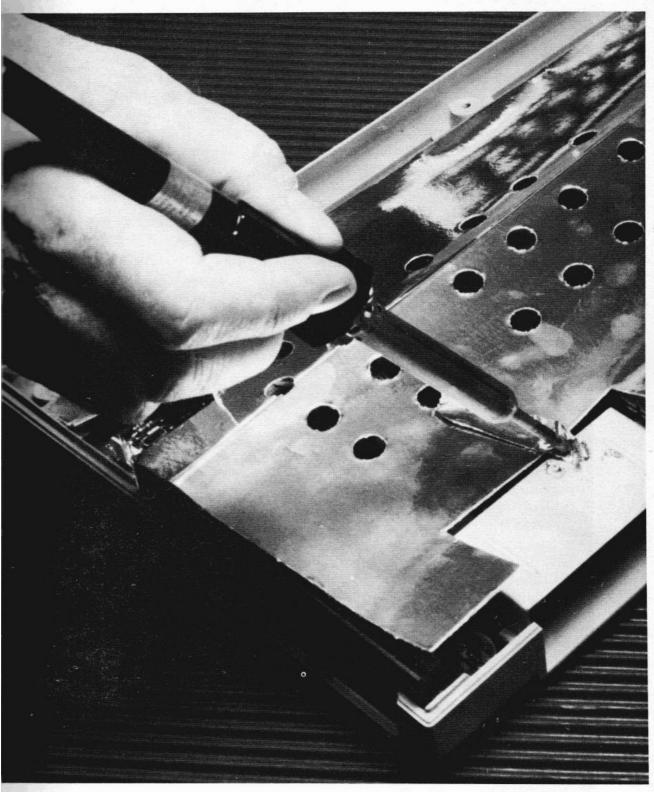

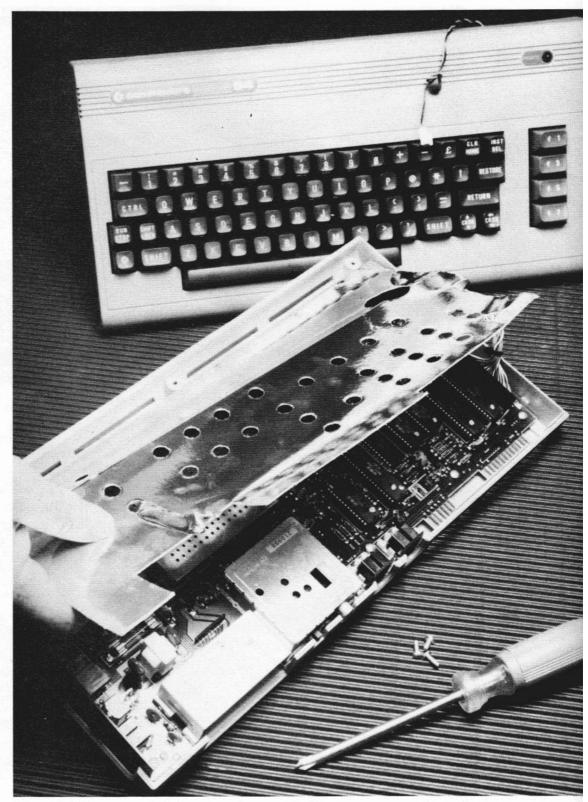

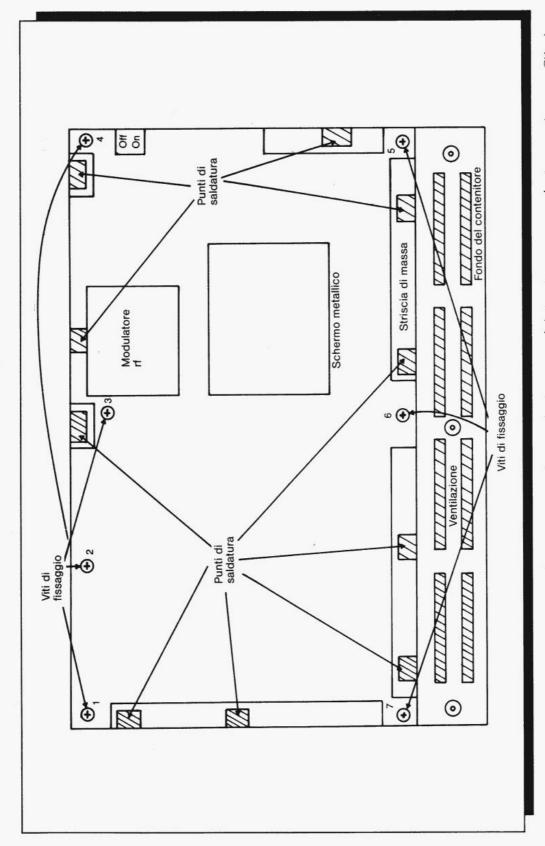

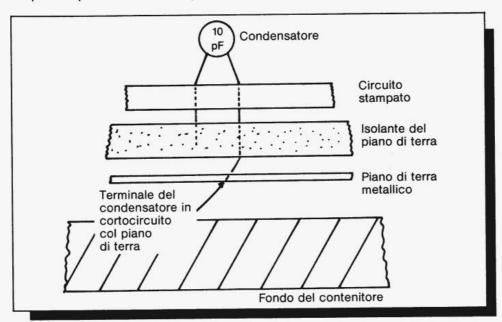

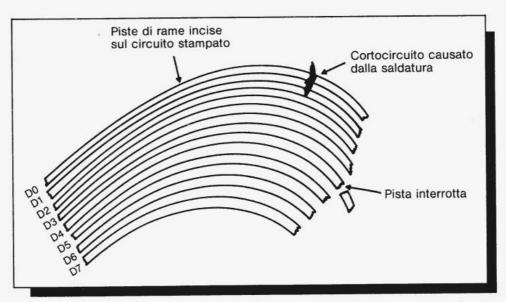

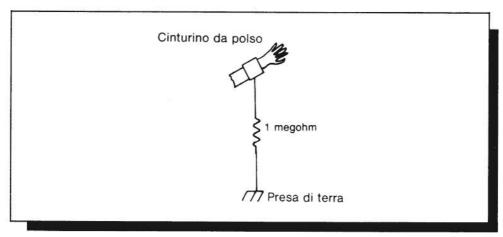

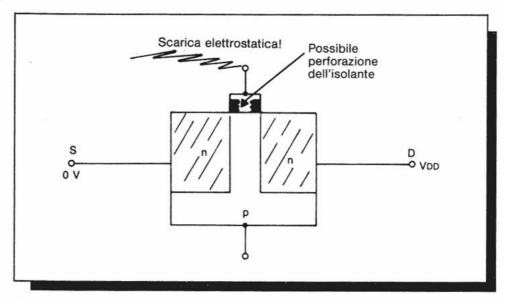

| Rimozione del coperchio 33 Rimozione della piastra del circuito stampato 34 Lo smontaggio come cura 45 Ispezione visiva 45 Cortocircuito col piano di terra 45 Difetti della piastra 45 Pulizia 45 Elettricità statica 46 Che cos'è? 46 Il cinturino da polso 47 Precauzioni supplementari 48                                                                                                                                                                                                                                                                                |

| Capitolo 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

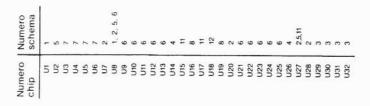

| Guida alla disposizione dei componenti 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

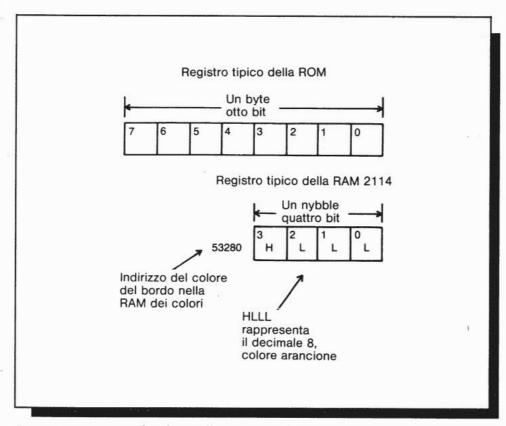

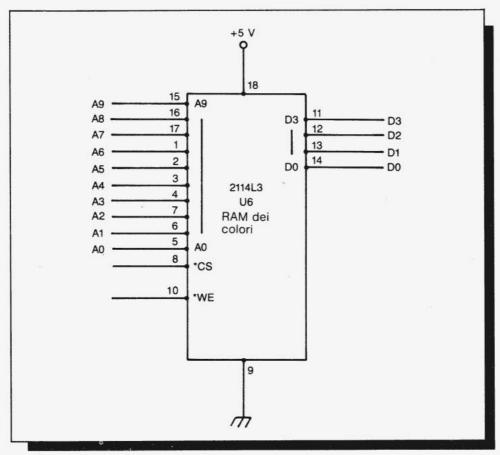

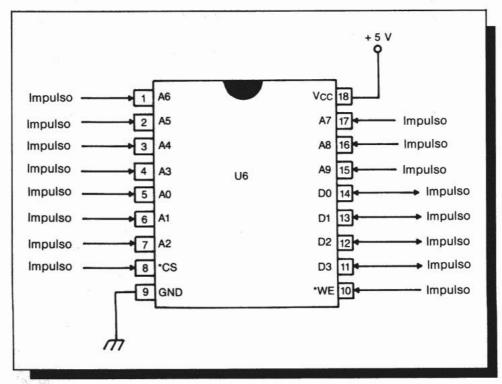

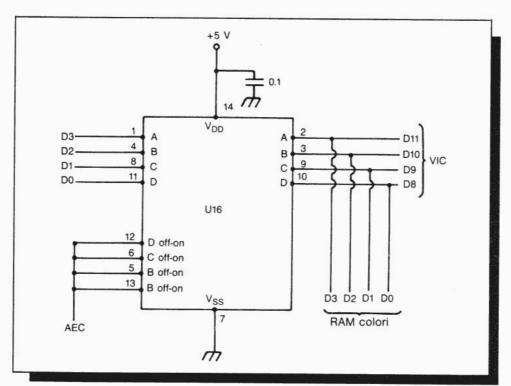

| Costruzione della guida 57 Panoramica dei chip 55 Il microprocessore (MPU) 55 Gli adattatori di interfaccia complessa (CIA) 56 Il chip di interfaccia video (VIC) 57 Il dispositivo di interfaccia per il suono (SID) 58 La memoria ad accesso casuale (RAM) 59 La memoria di sola lettura (ROM) del BASIC 60 La memoria di sola lettura (ROM) del Kernal 60 La memoria di sola lettura (ROM) dei caratteri 61 La memoria ad accesso casuale (RAM) dei colori 62 Altri componenti principali della piastra 63 Zoccoli 64 Uso della guida alla disposizione dei componenti 66 |

| Capitolo 4  Tecniche per la sostituzione dei chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

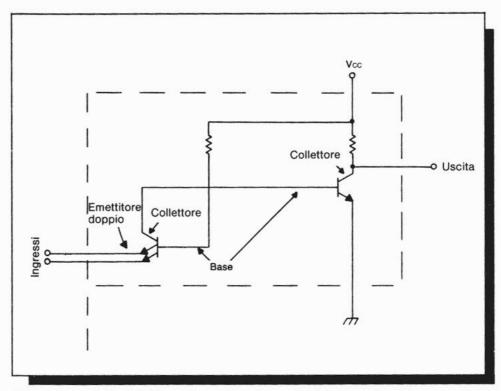

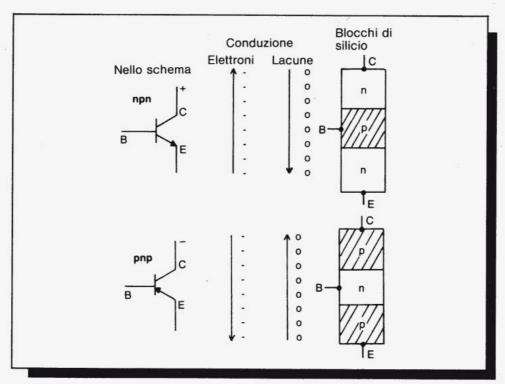

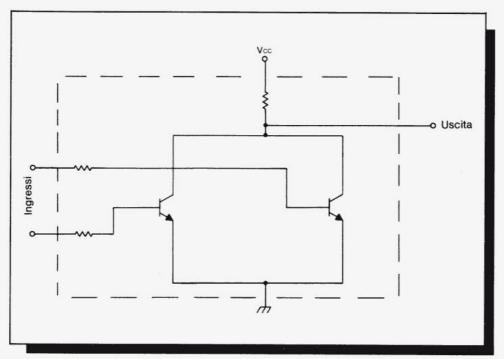

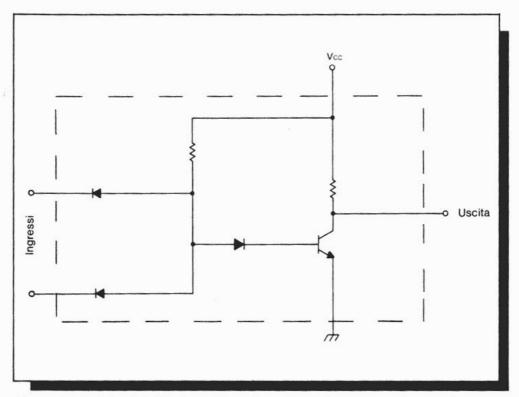

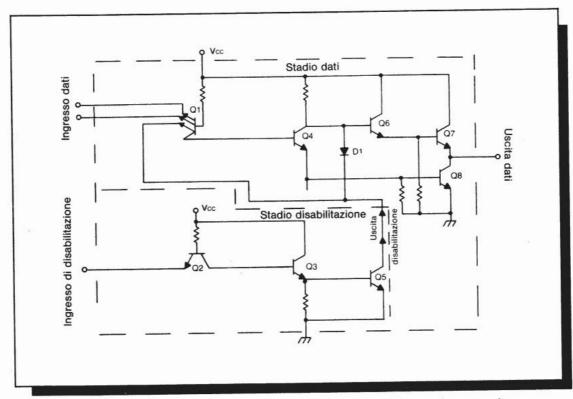

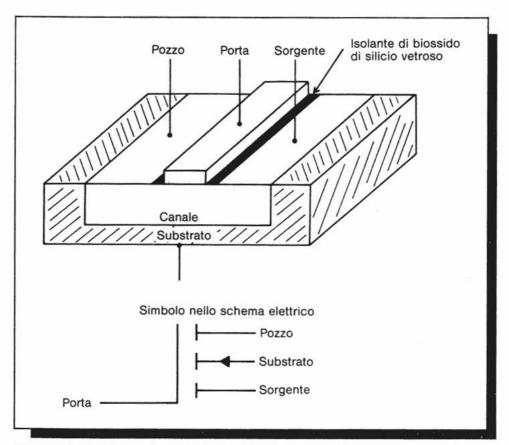

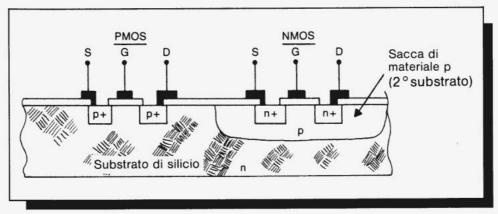

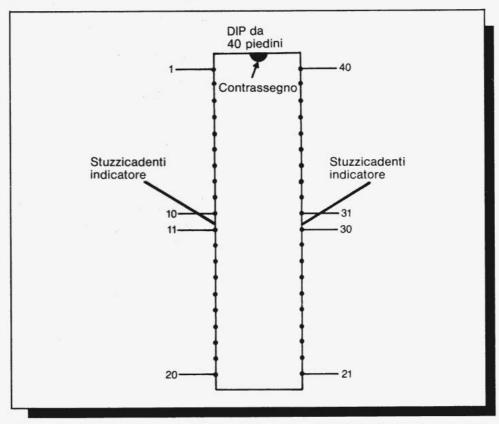

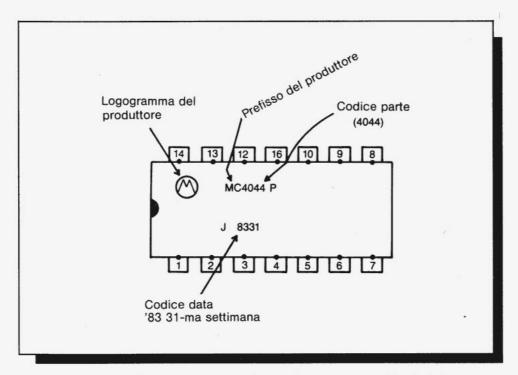

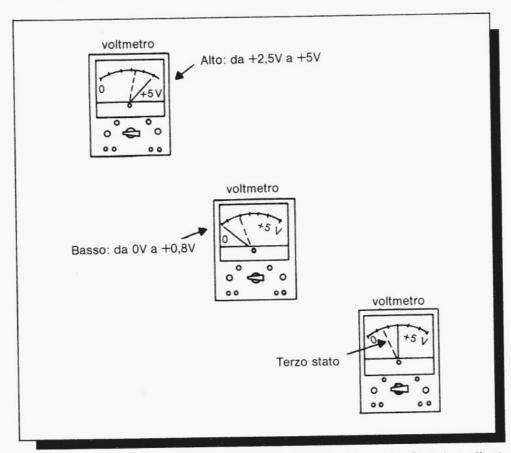

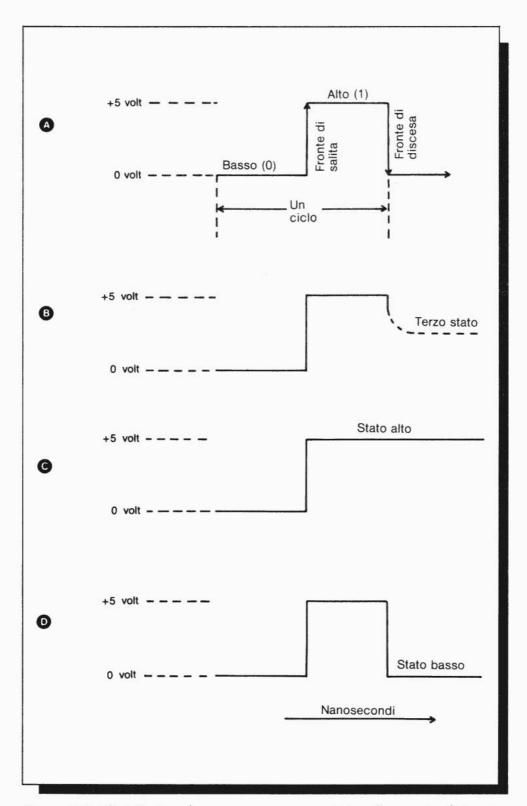

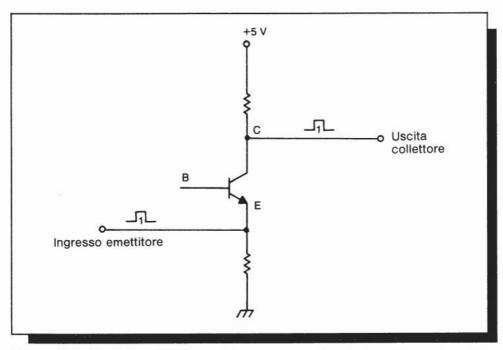

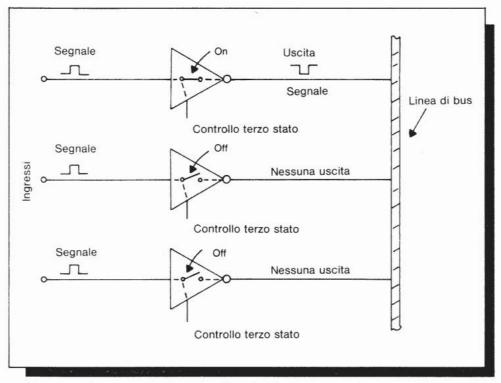

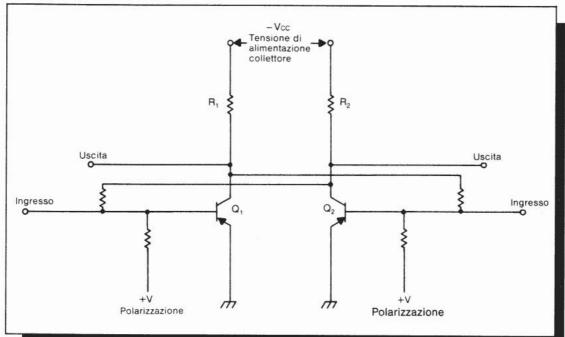

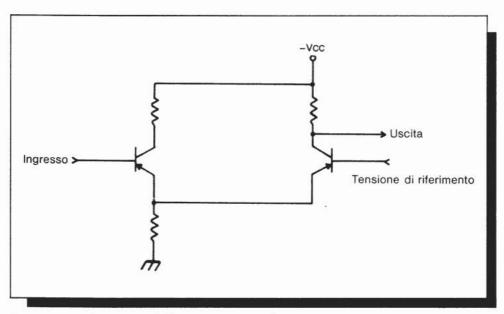

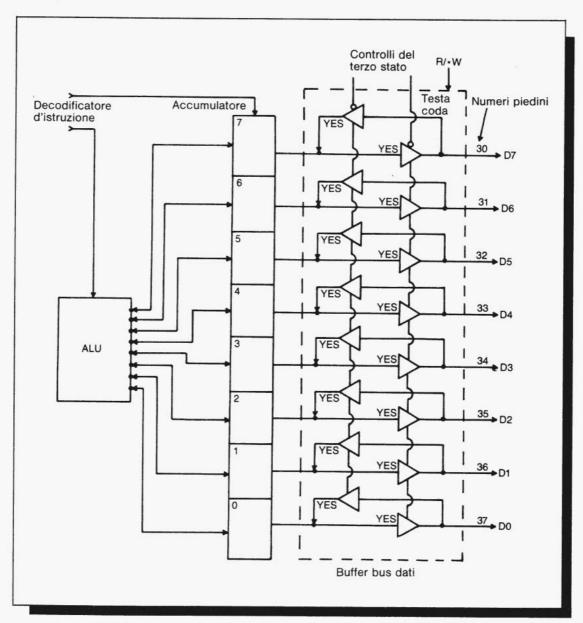

| TTL, DTL e RTL 70 TTL a tre stati 74 Chip MOS 77 Il contenitore DIP 87 Chip montati su zoccoli 84 Rimozione dei chip 87 Sostituzione dei chip 86 Chip saldati sulla piastra 88 Dissaldatura 88 Risaldatura 90                                                                                                                                                                                                                                                                                                                                                                |

| Capitolo 5                                                                                                                                                                                                                                                                                                                                   |                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Chip LSI                                                                                                                                                                                                                                                                                                                                     | 93                                                          |

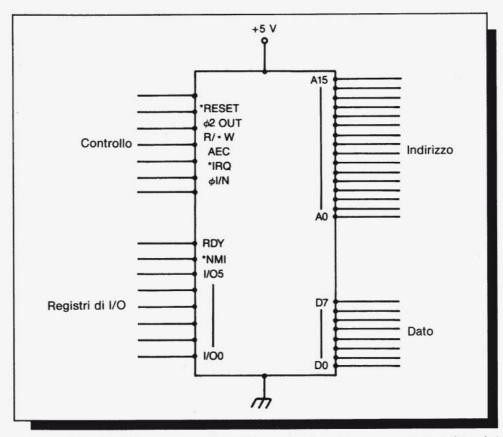

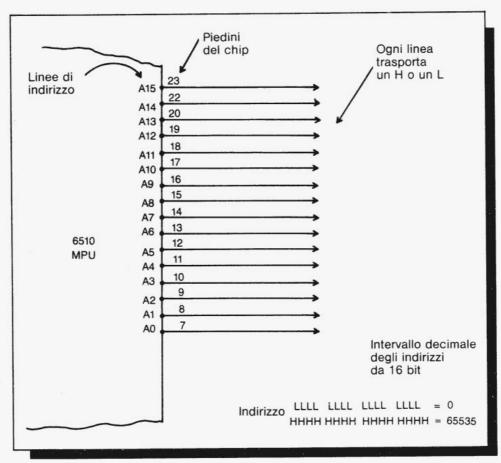

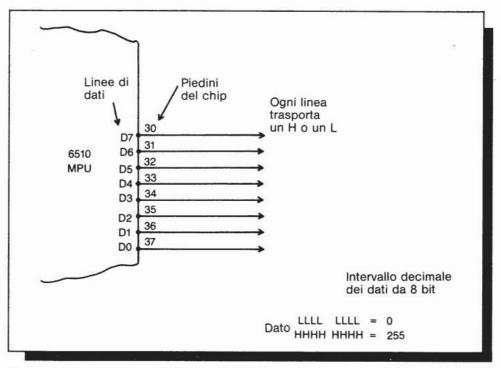

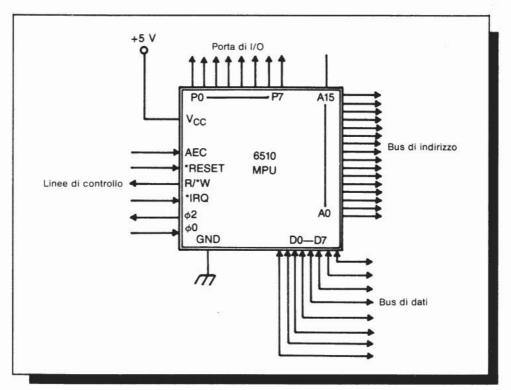

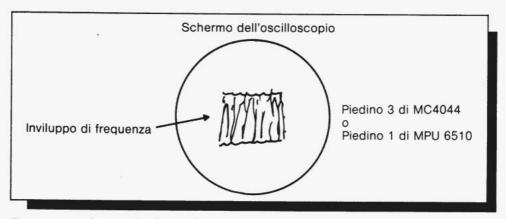

| Il microprocessore (MPU) 6510                                                                                                                                                                                                                                                                                                                | 94<br>98<br>105<br>109                                      |

| Capitolo 6                                                                                                                                                                                                                                                                                                                                   |                                                             |

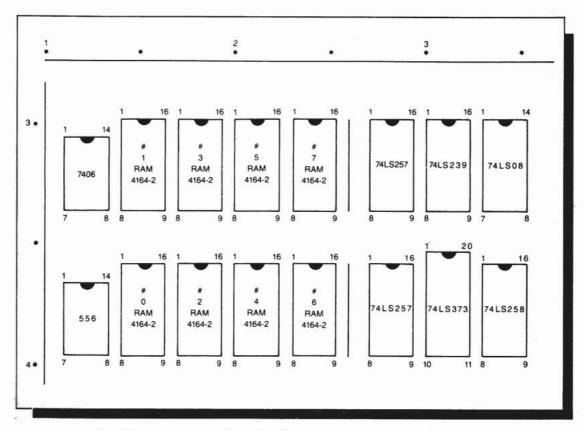

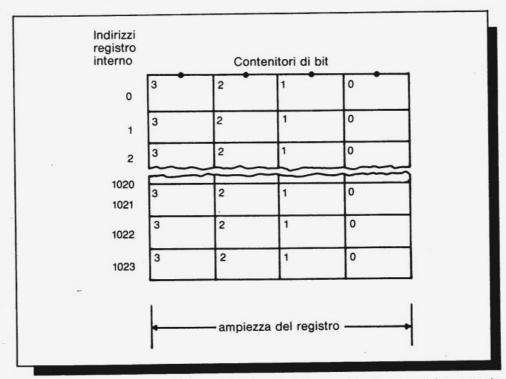

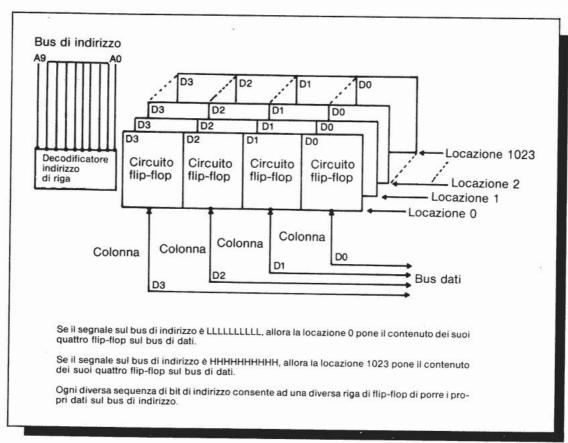

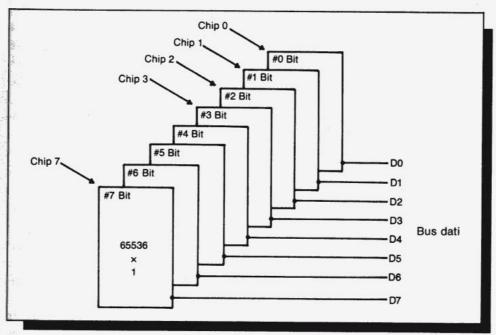

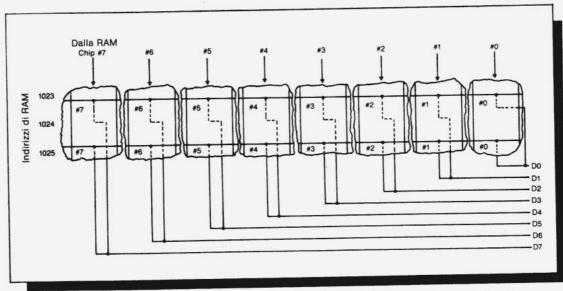

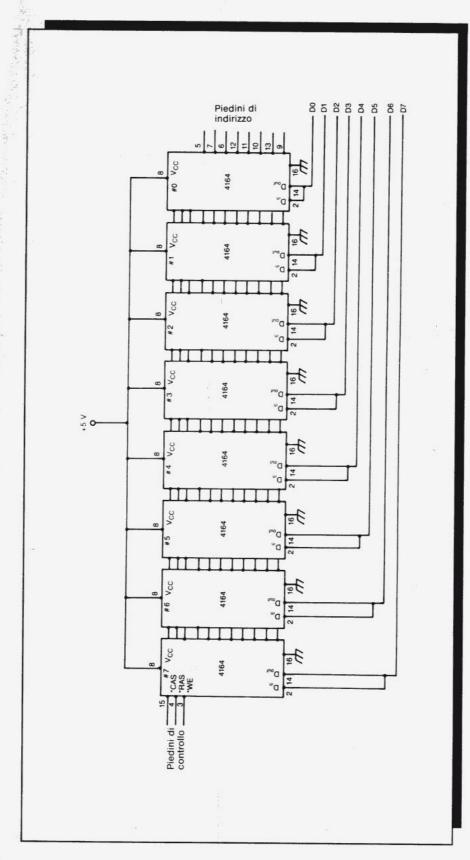

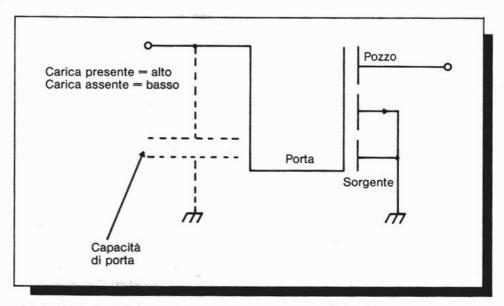

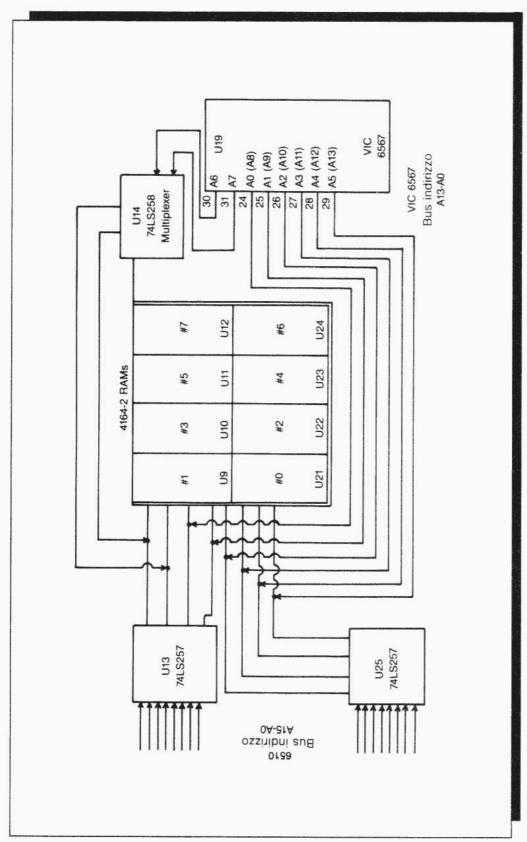

| La memoria ad accesso casuale (RAM)                                                                                                                                                                                                                                                                                                          | 113                                                         |

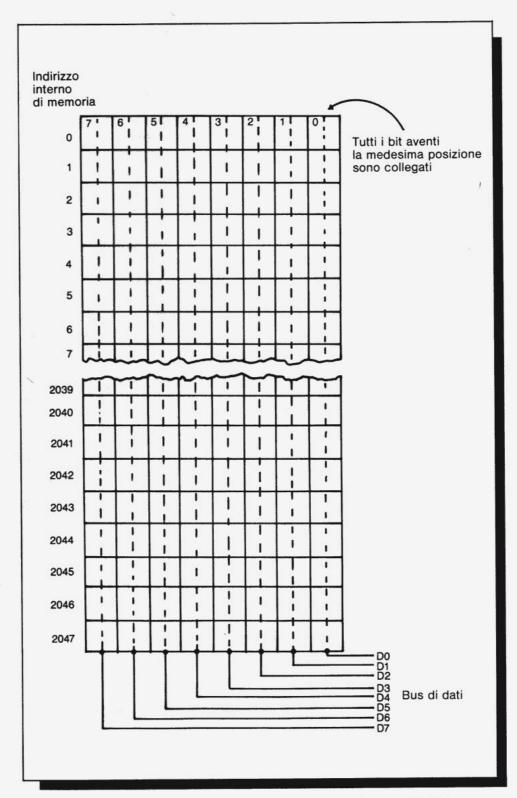

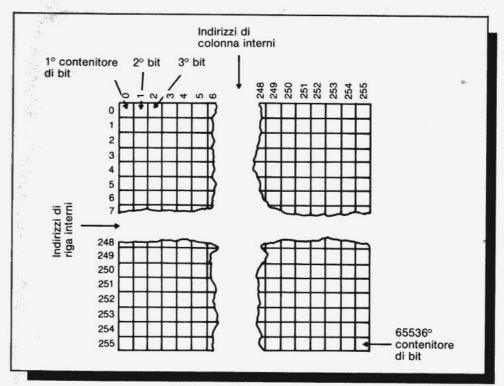

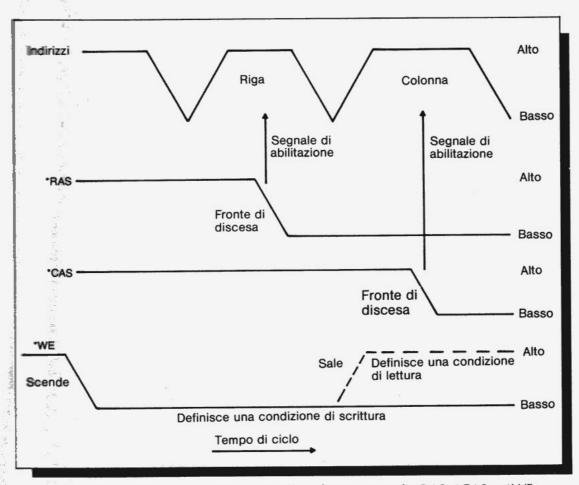

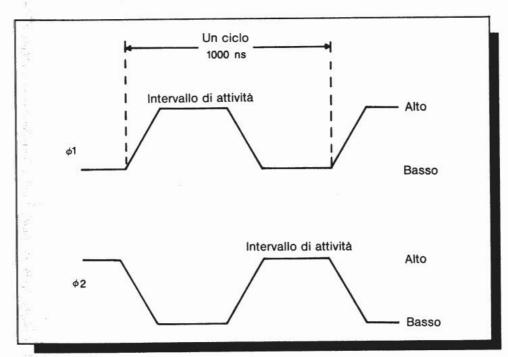

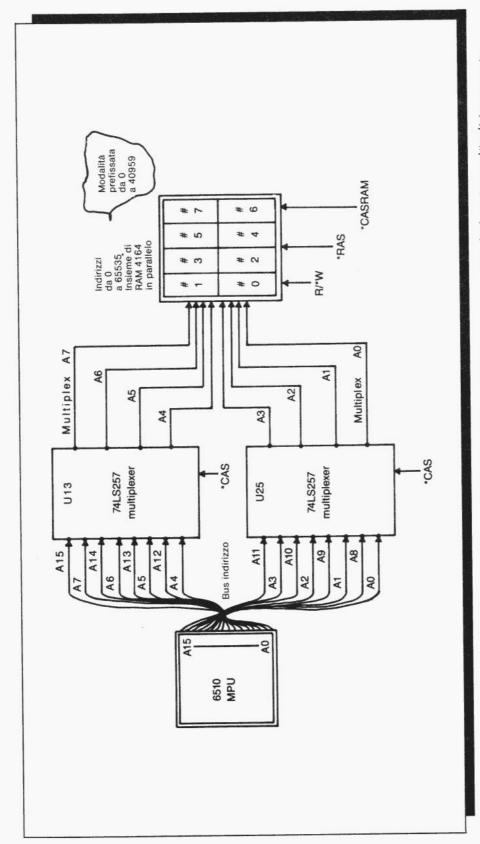

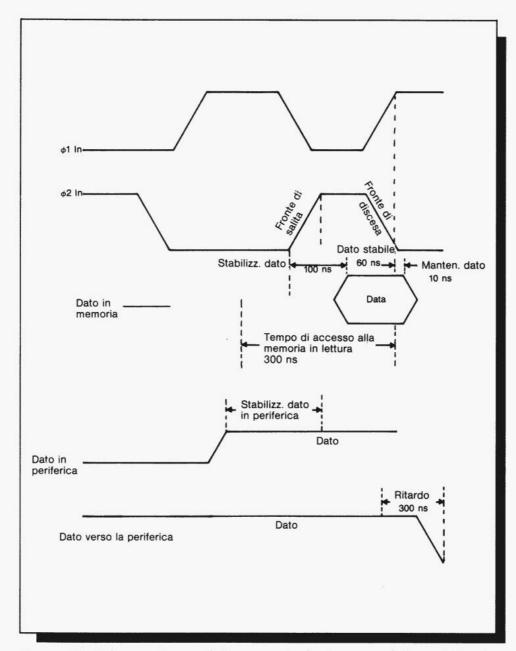

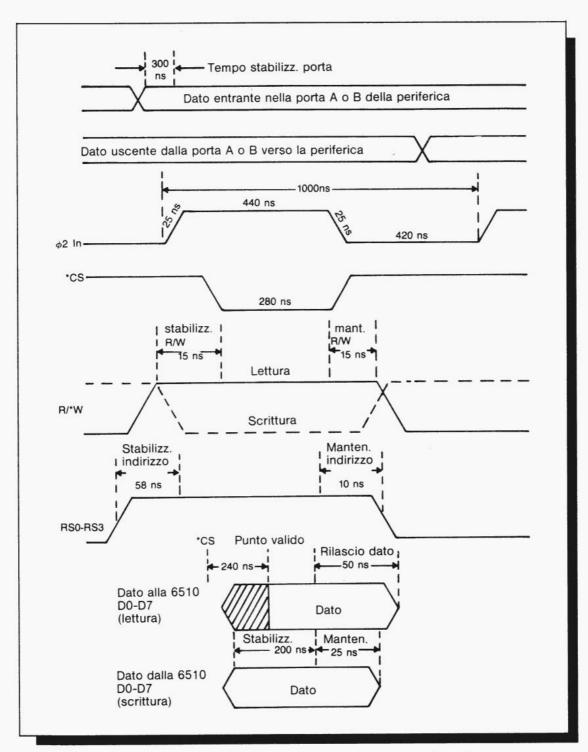

| RAM statica RAM dinamica Ristoro della memoria Configurazione della memoria Funzionamento Temporizzazione Temporizzazione di ristoro della RAM dinamica                                                                                                                                                                                      | 115<br>119<br>124<br>125<br>128<br>130<br>132               |

| Capitolo 7                                                                                                                                                                                                                                                                                                                                   |                                                             |

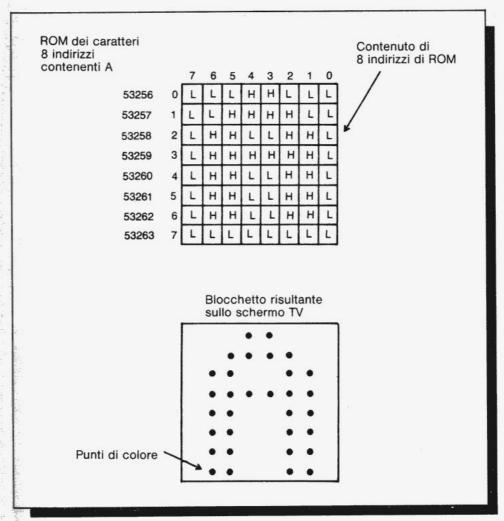

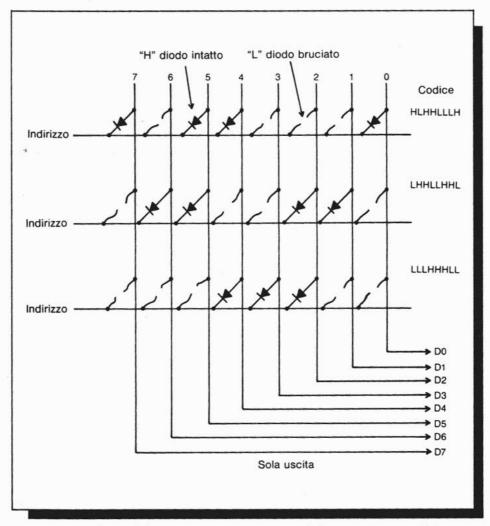

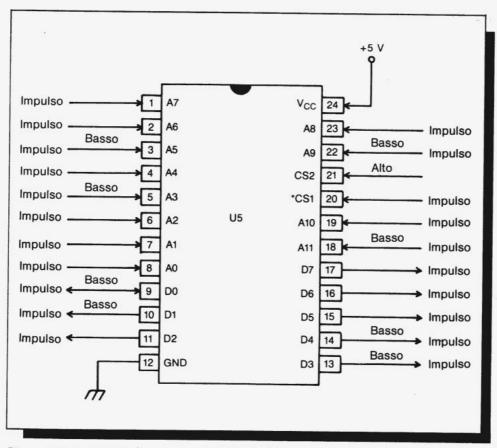

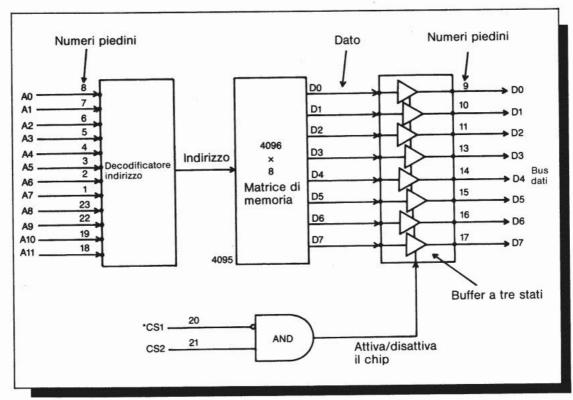

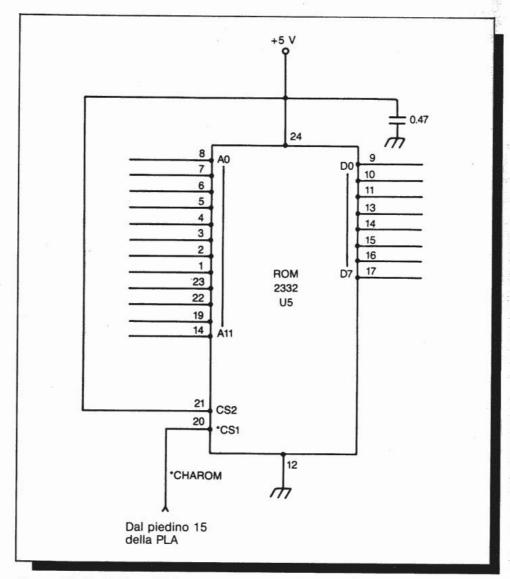

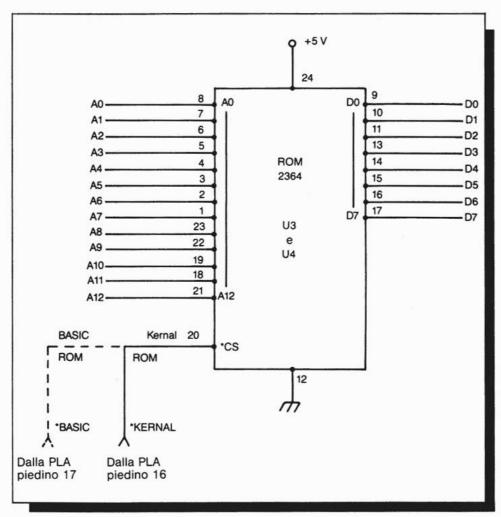

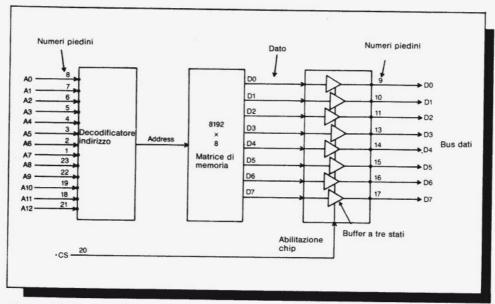

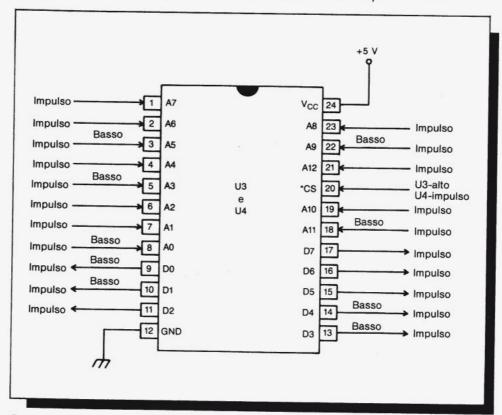

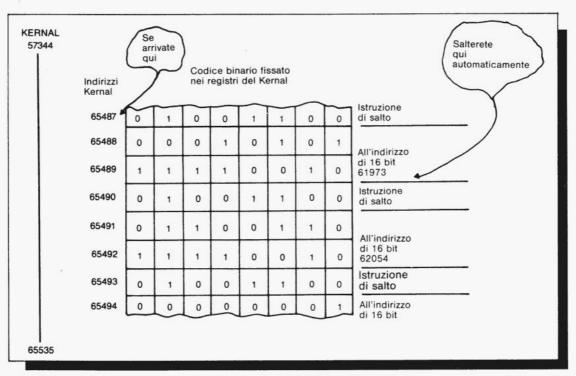

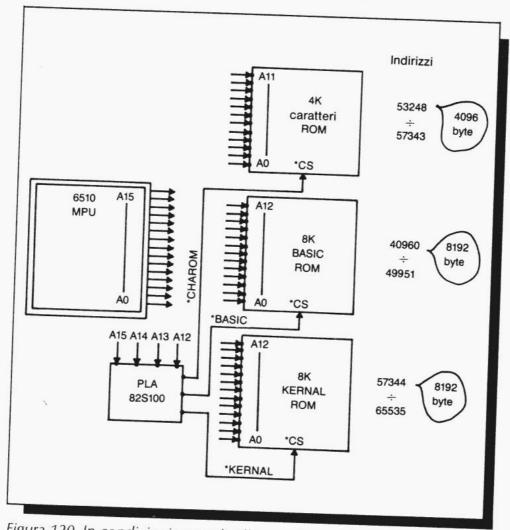

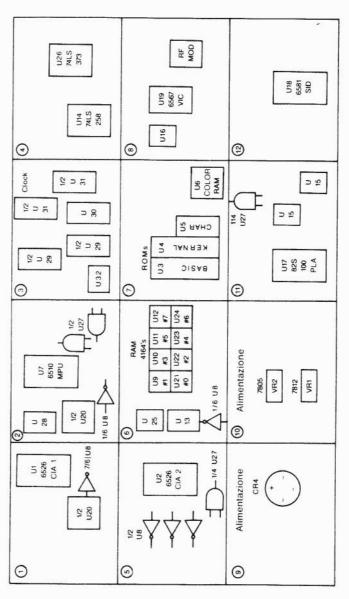

| La memoria di sola lettura (ROM)                                                                                                                                                                                                                                                                                                             | 135                                                         |

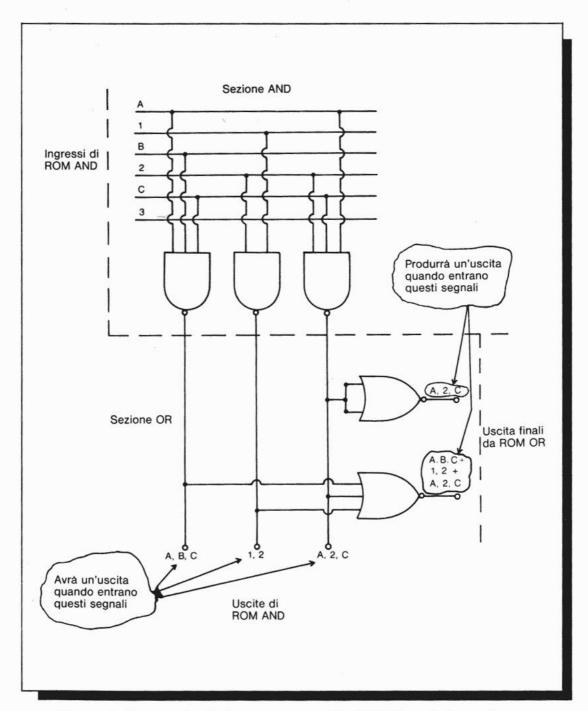

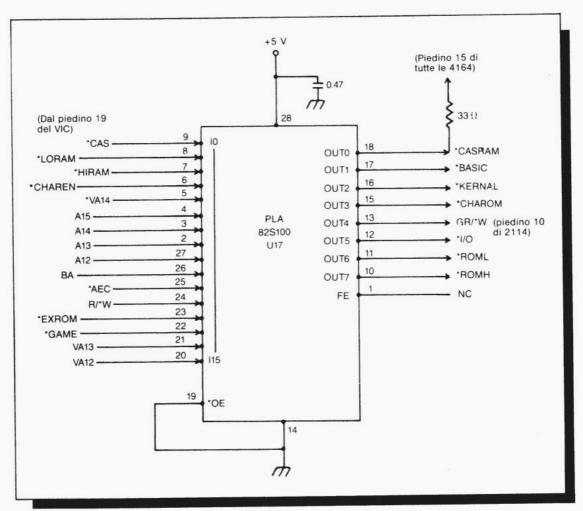

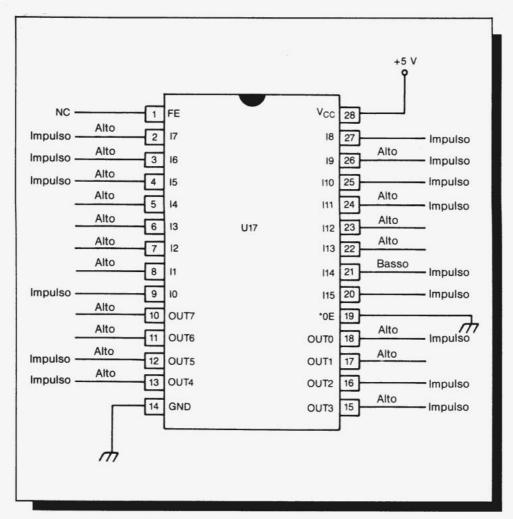

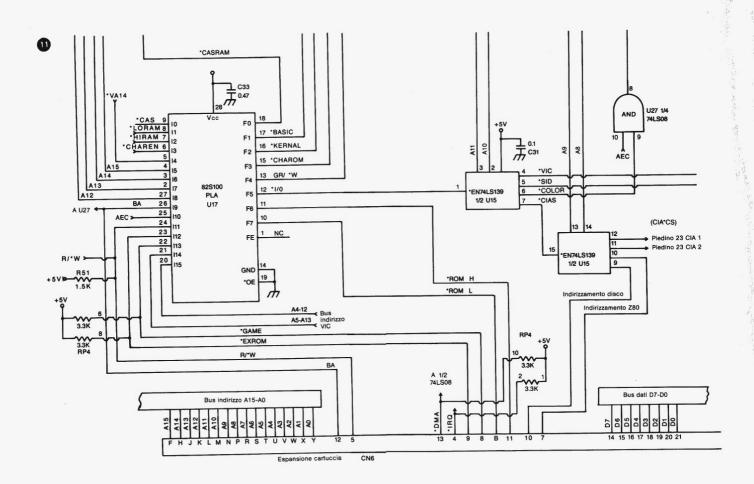

| Diagramma a blocchi La ROM dei caratteri Le ROM del Kernal e del BASIC La ROM del BASIC La ROM del Kernal Tabelle di salto La matrice logica programmabile (PLA) Piedinatura del chip 82S100 Ingressi della PLA Diagrammi per la ricerca dei guasti                                                                                          | 138<br>143<br>144<br>147<br>148<br>149<br>151<br>153<br>155 |

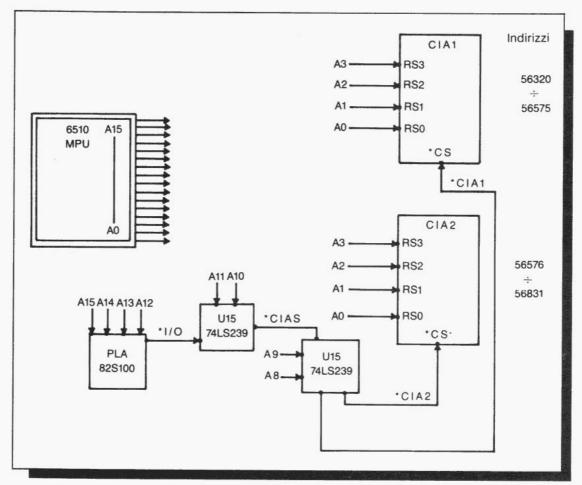

| Capitolo 8 Altri circuiti integrati                                                                                                                                                                                                                                                                                                          | 161                                                         |

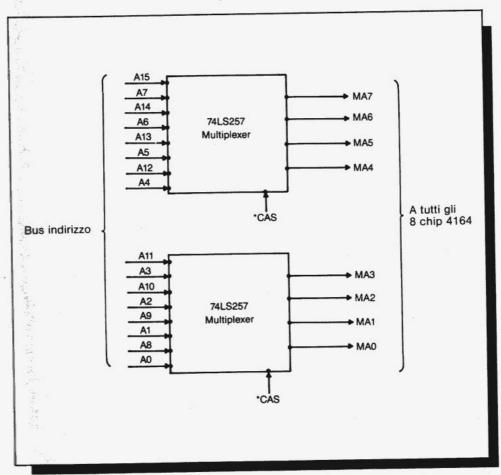

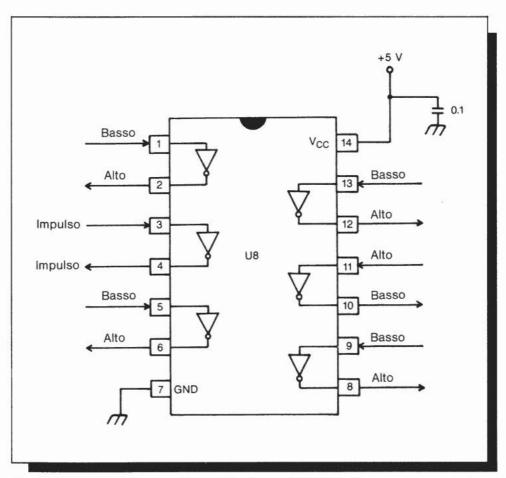

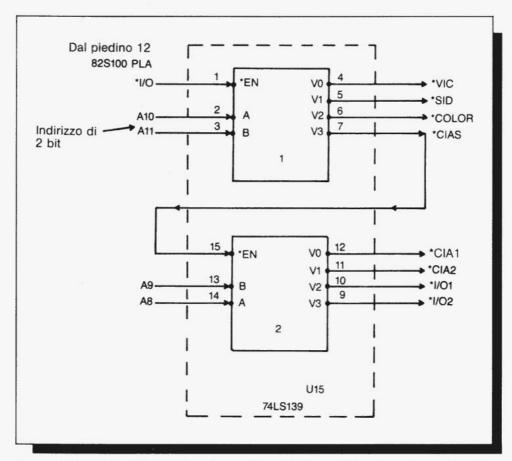

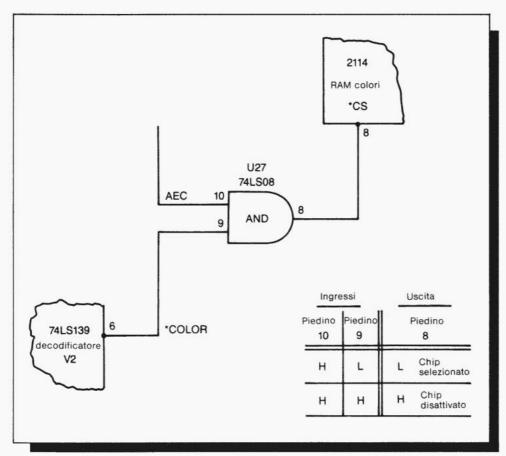

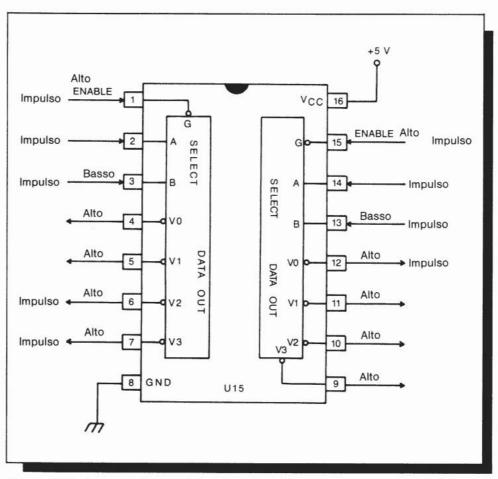

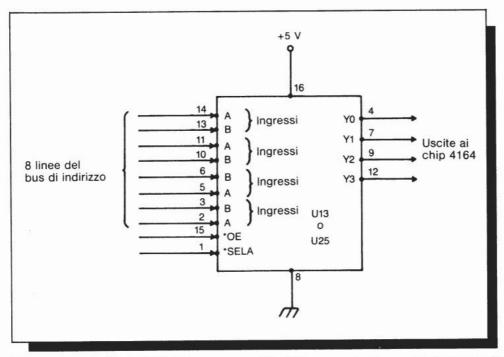

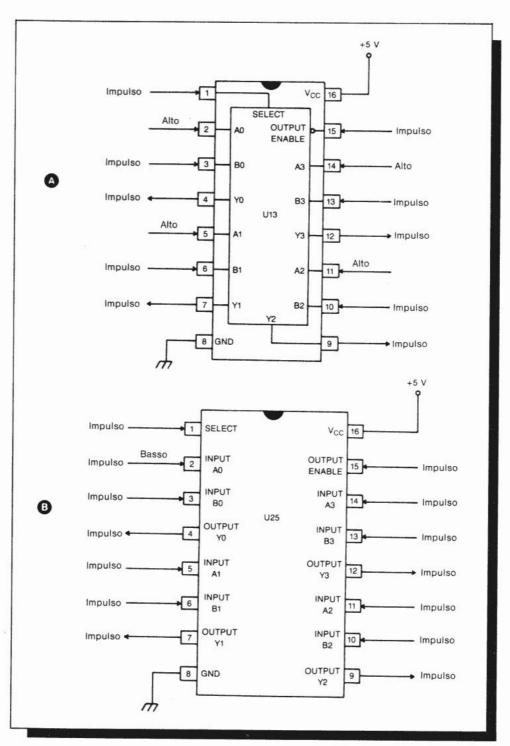

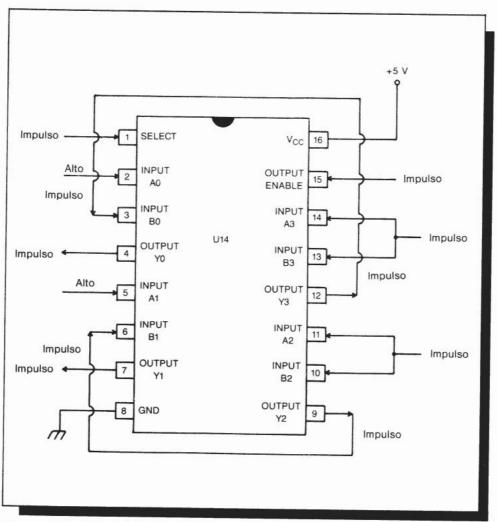

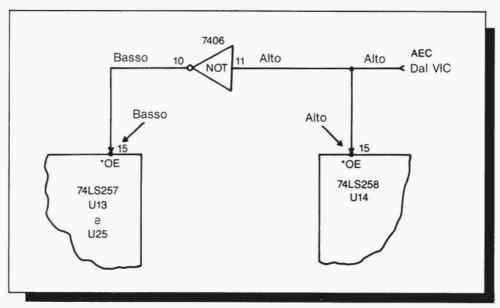

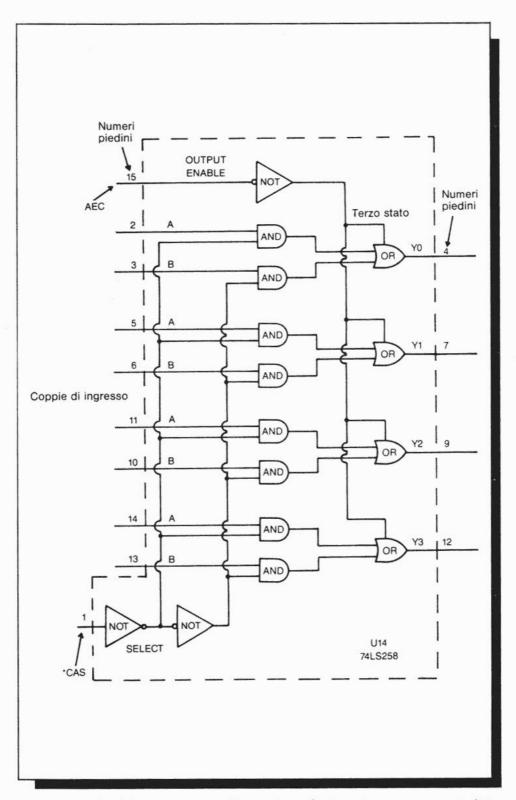

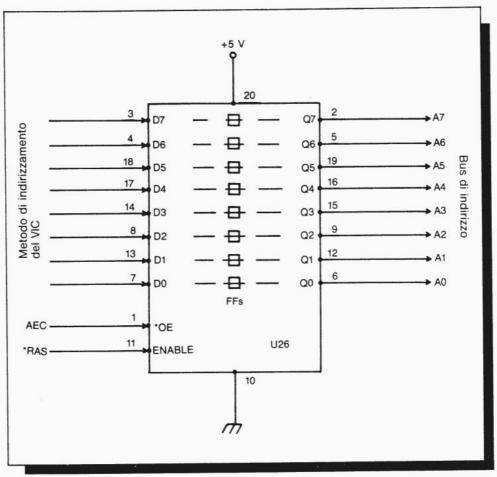

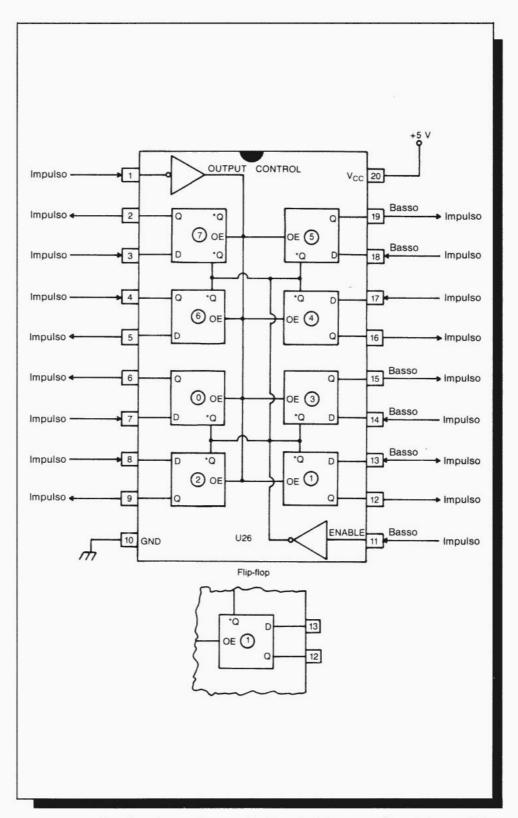

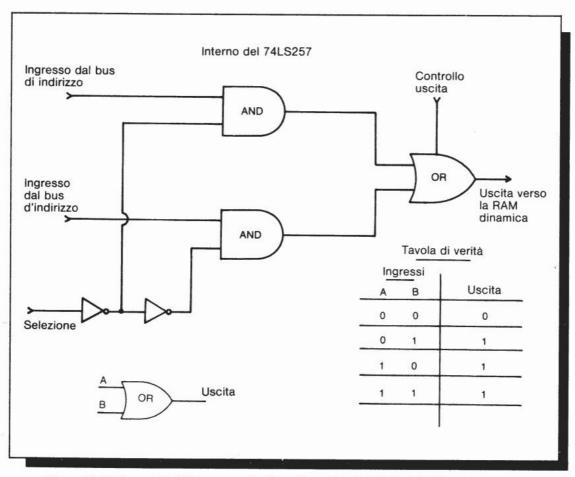

| L'invertitore hex 7406N  La porta AND quadrupla a due ingressi 74LS08  Il flip-flop D duale 74LS74  Il contatore diretto/inverso 74LS193  Il decodificatore da 2 a 4 linee 74LS139  Il multiplexer quadruplo a due ingressi 74LS257  Il multiplexer quadruplo a due ingressi 74LS258  Il registro-tampone ("latch") ottale di tipo D 74LS373 | 161<br>164<br>167<br>171<br>173<br>177<br>179<br>184        |

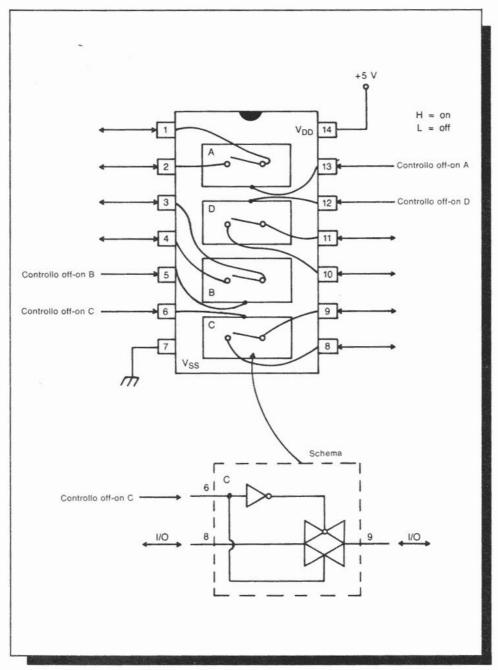

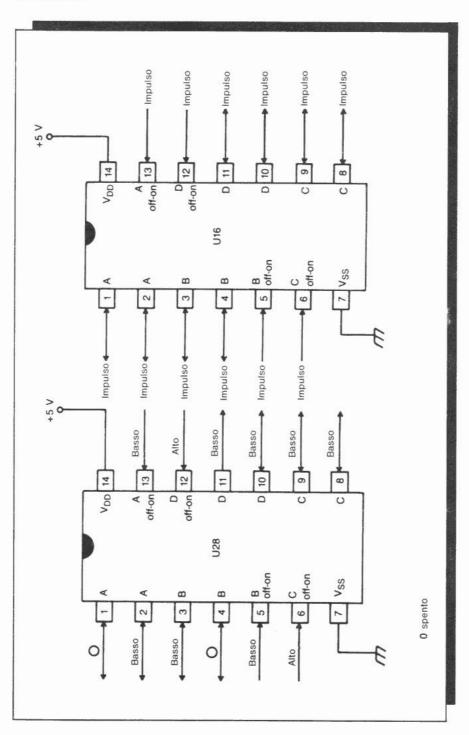

| L'interruttore bilaterale quadruplo 4066                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 186<br>190<br>192                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Capitolo 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                        |

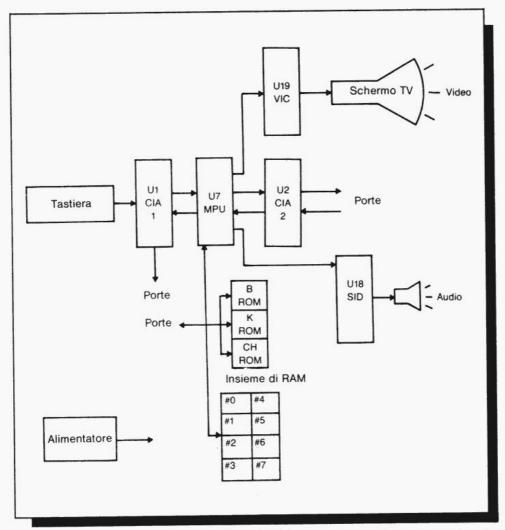

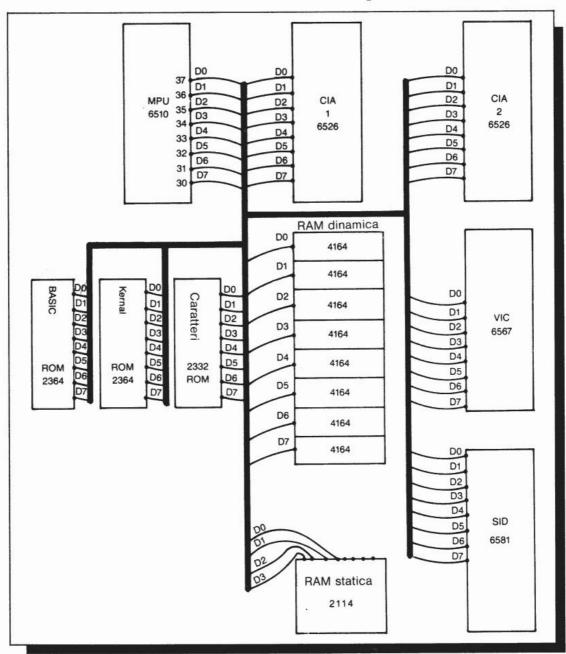

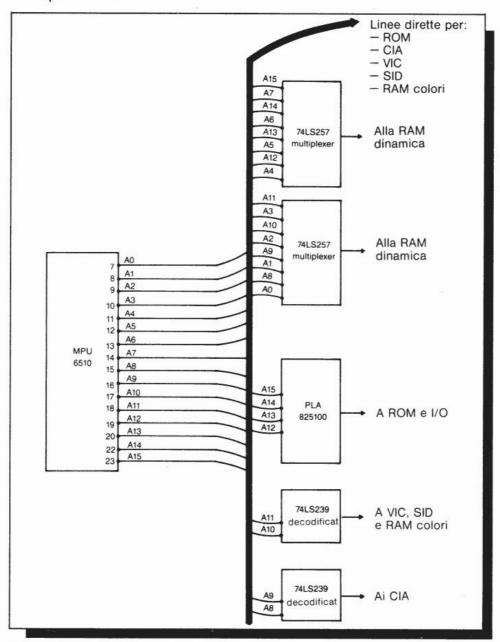

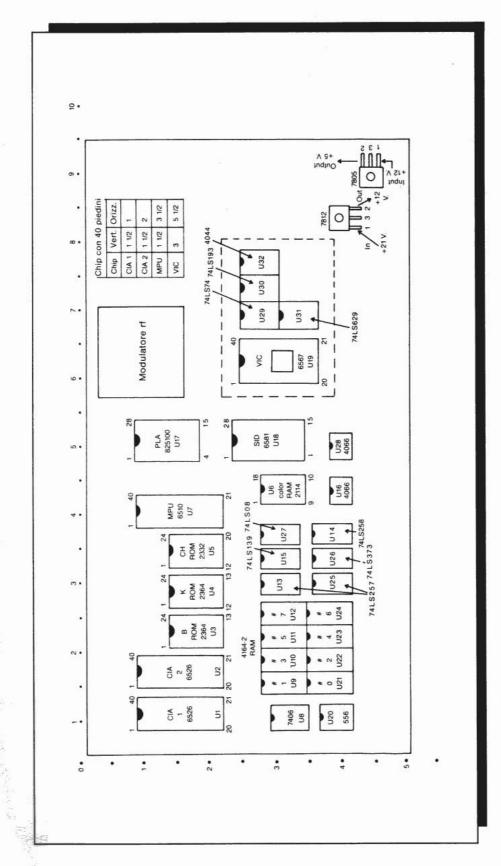

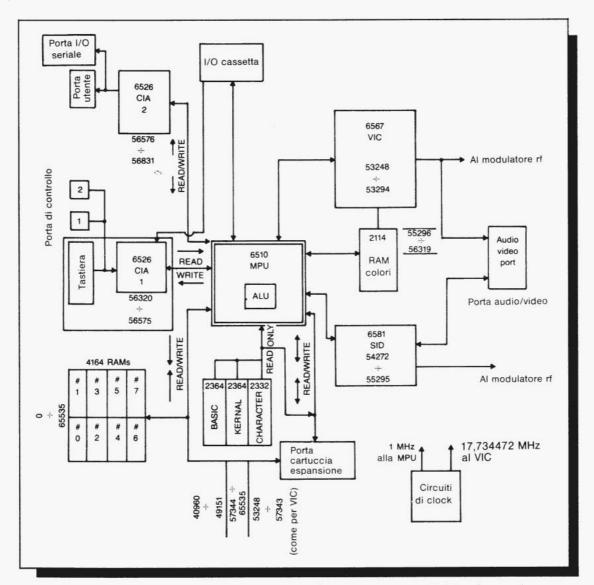

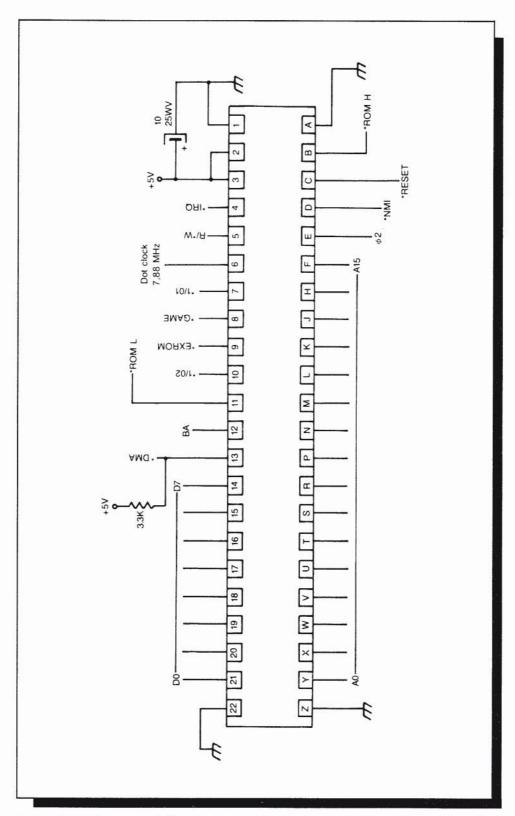

| Diagramma a blocchi del sistema                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 195                                    |

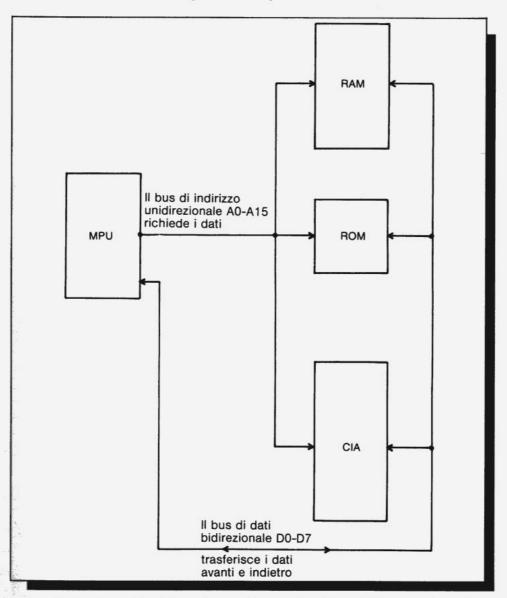

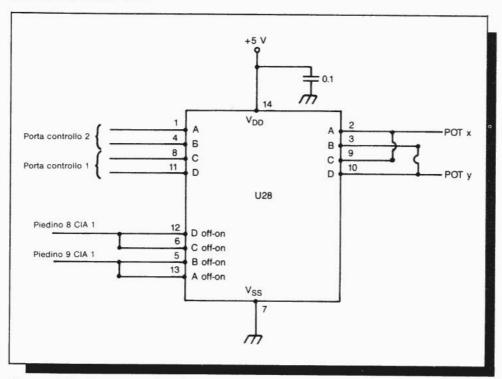

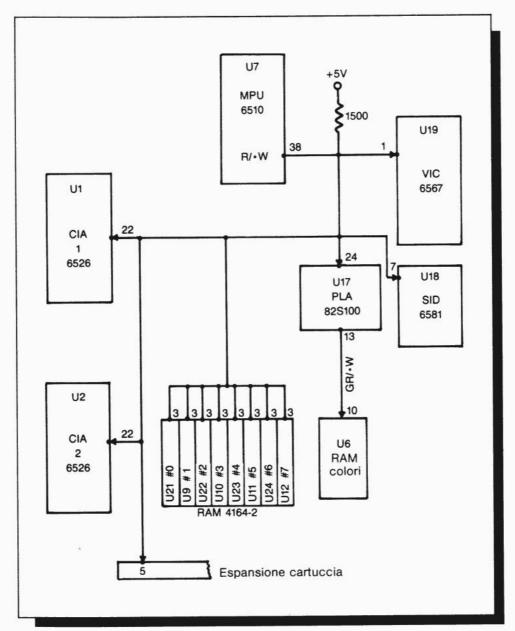

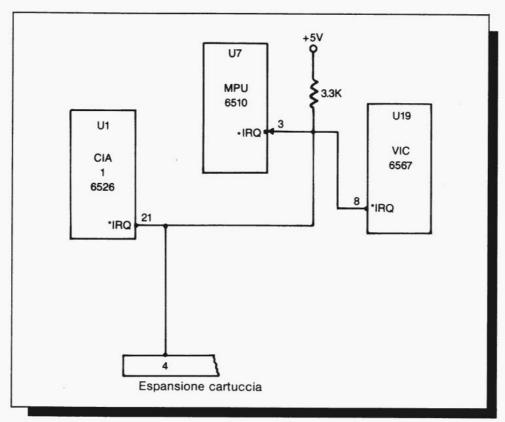

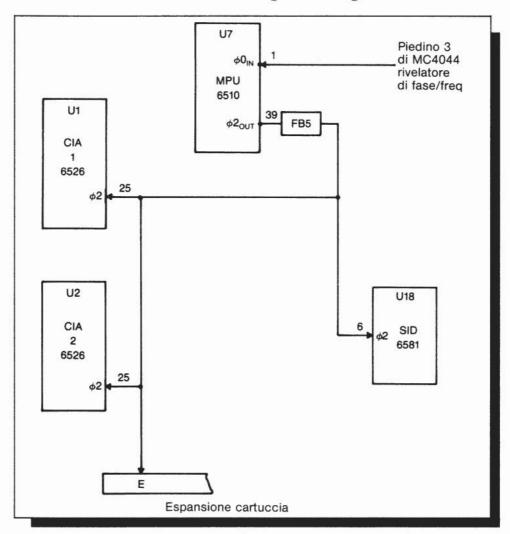

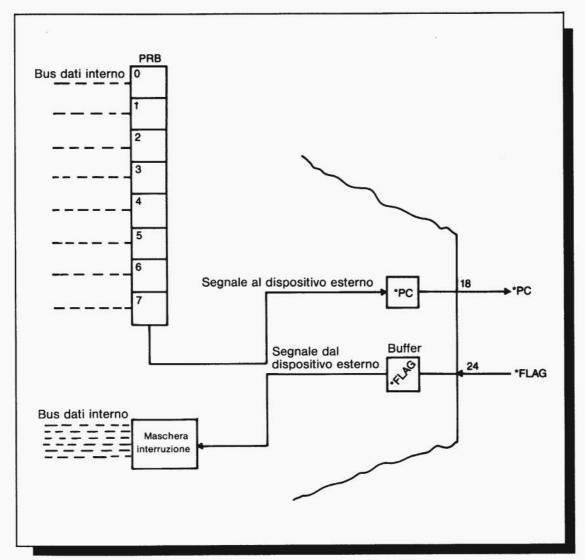

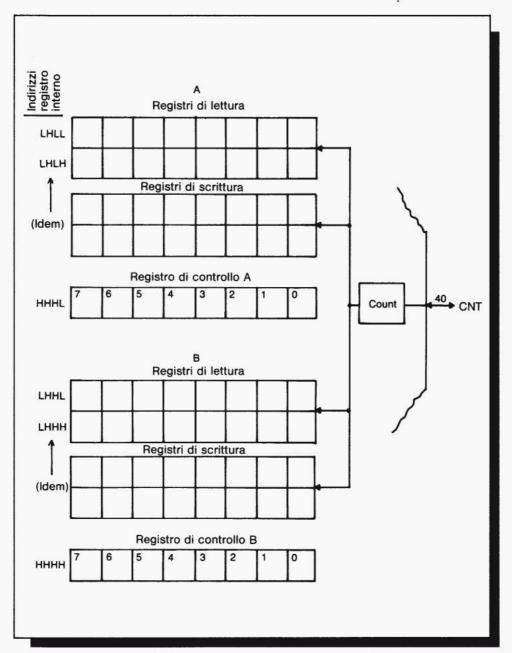

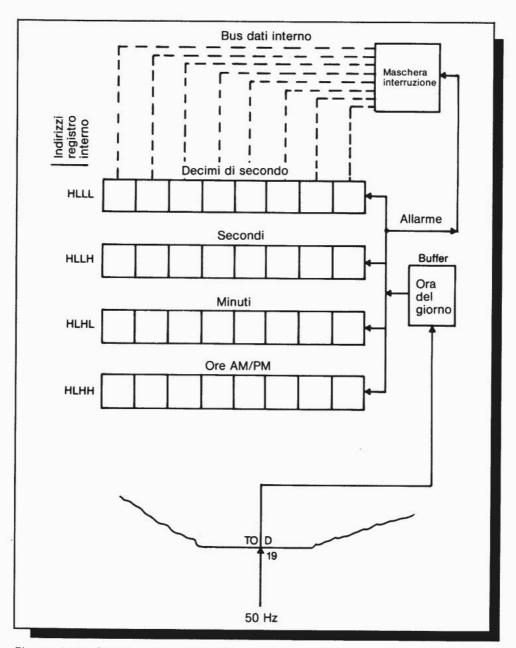

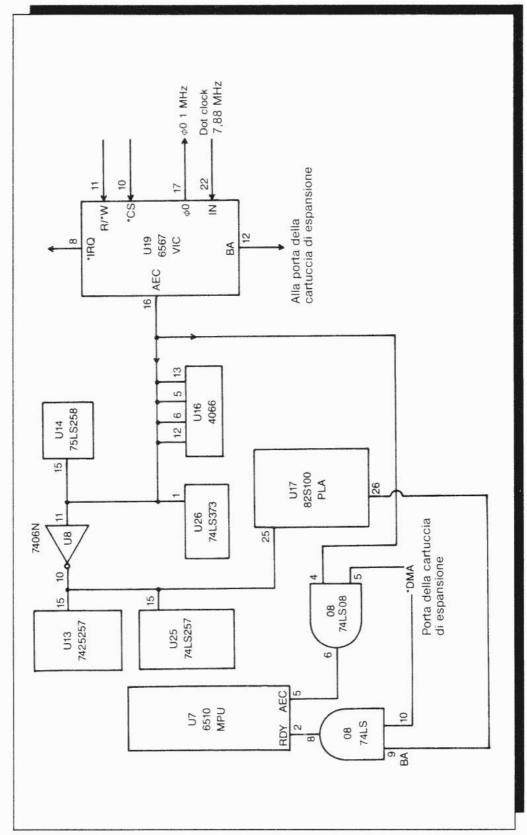

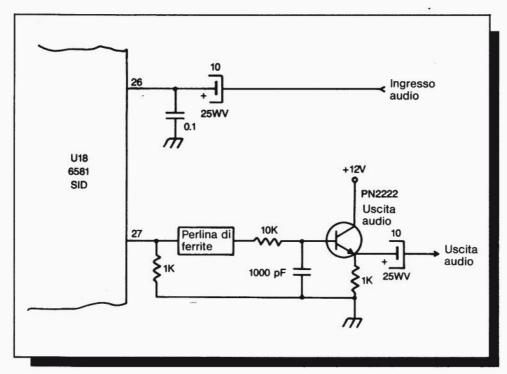

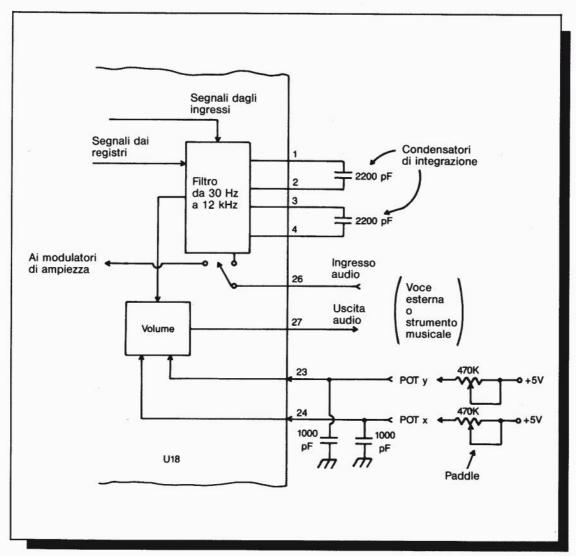

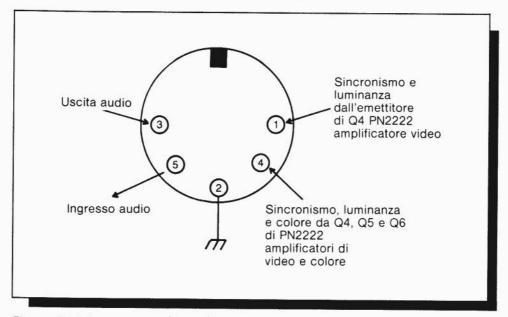

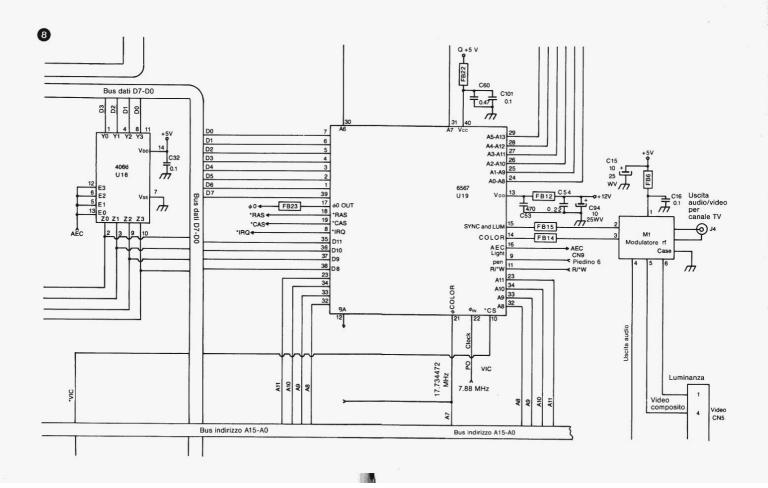

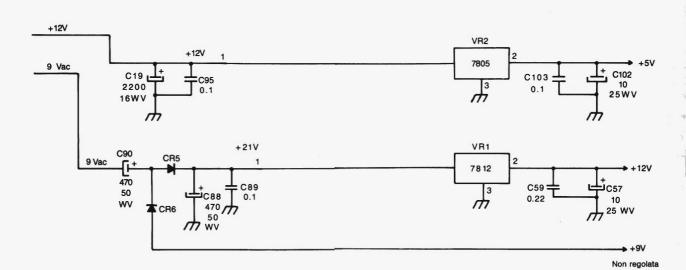

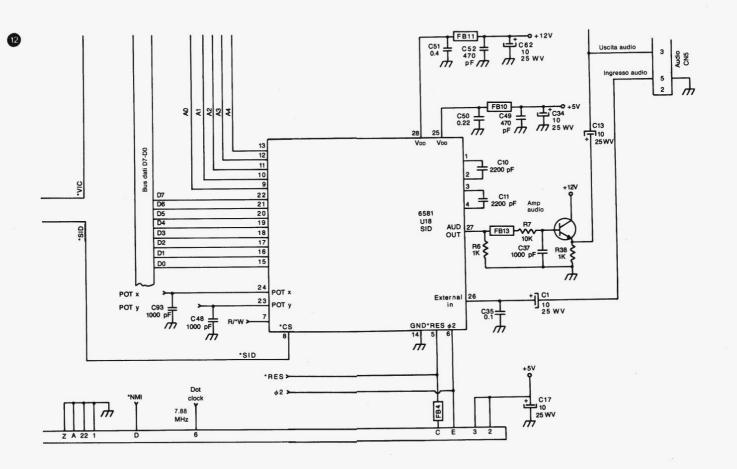

| Diagramma a blocchi La MPU e la RAM dinamica La MPU e la ROM La MPU e l'interfaccia CIA La MPU ed il VIC II La MPU ed il SID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 195<br>198<br>202<br>204<br>206<br>211 |

| Caritala 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |

| Capitolo 10 Ricerca e riparazione dei guasti nelle porte logiche                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 215                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

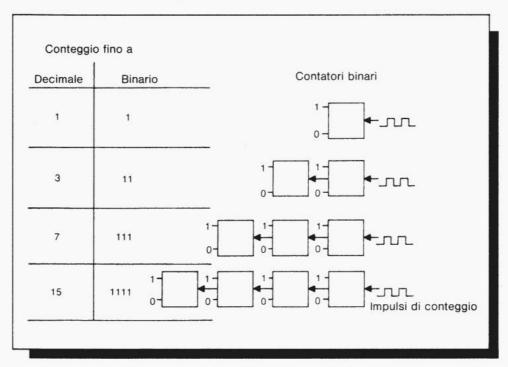

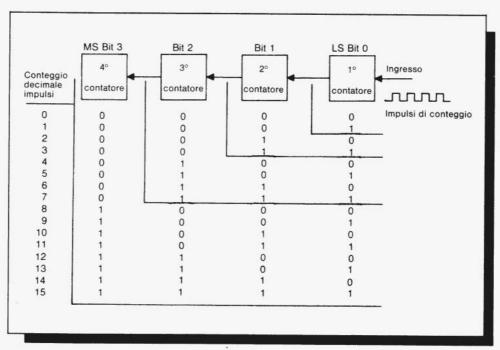

| Decimale e binario                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 215                                    |

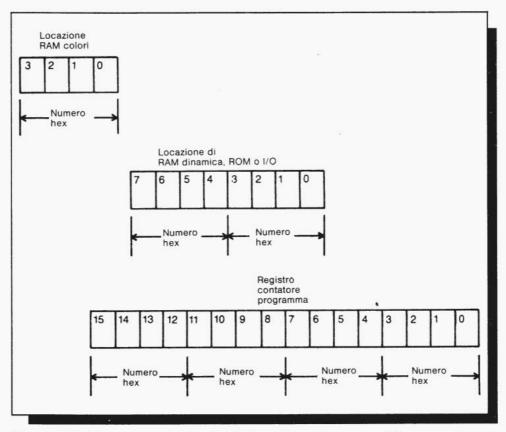

| Esadecimale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 220<br>222                             |

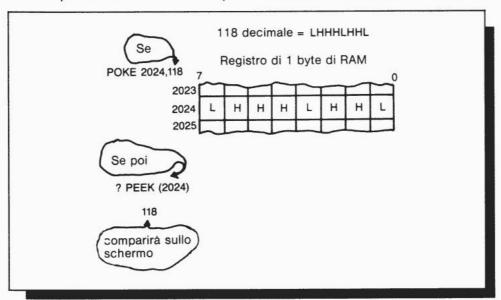

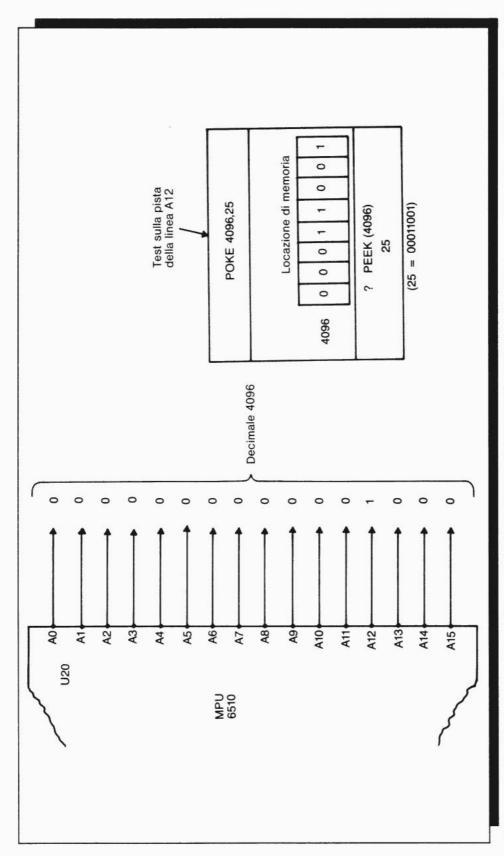

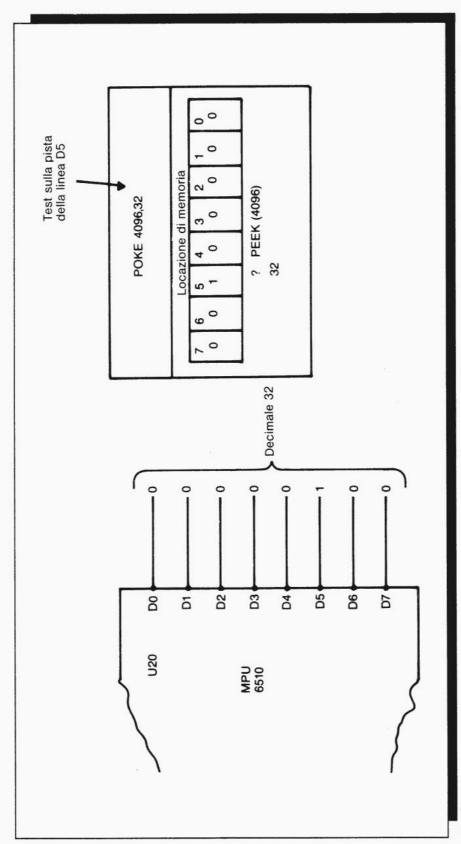

| PEEK e POKE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 223                                    |

| Porte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 227                                    |

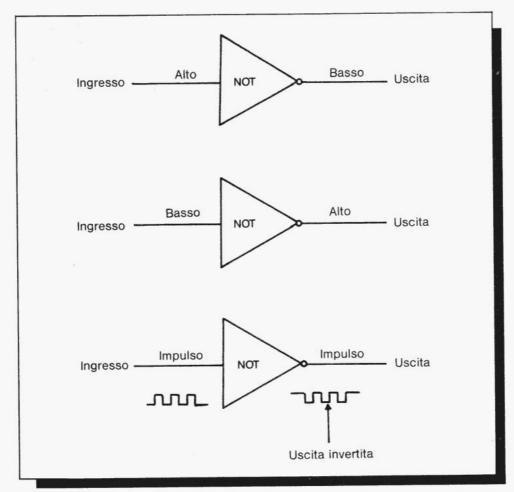

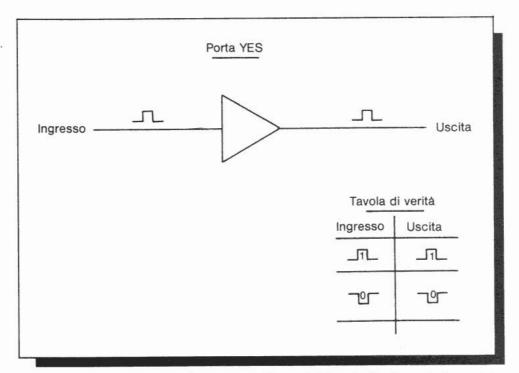

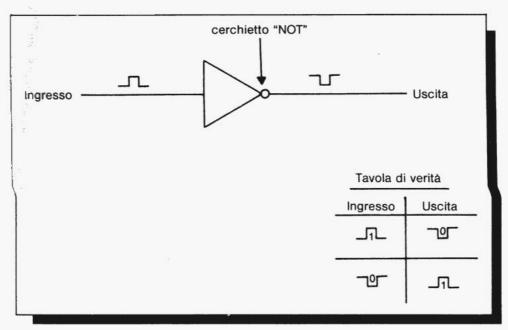

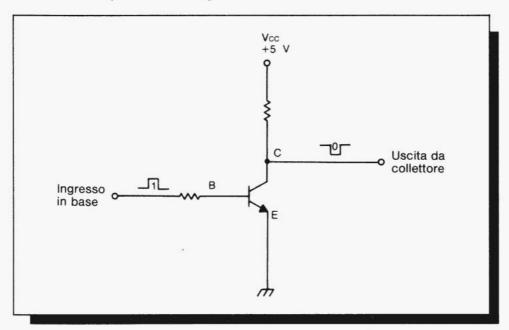

| La porta YES<br>La porta NOT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 230                                    |

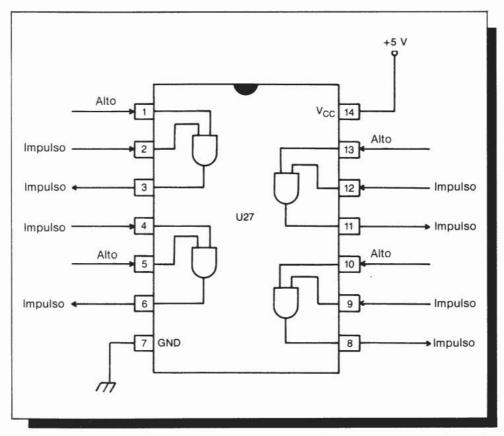

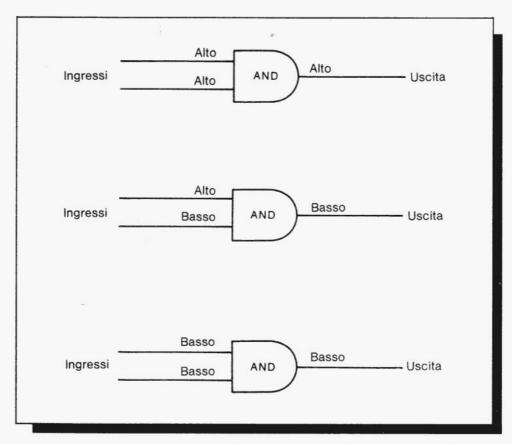

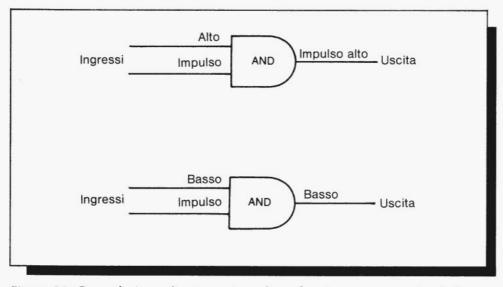

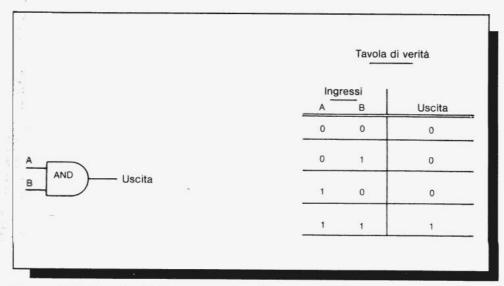

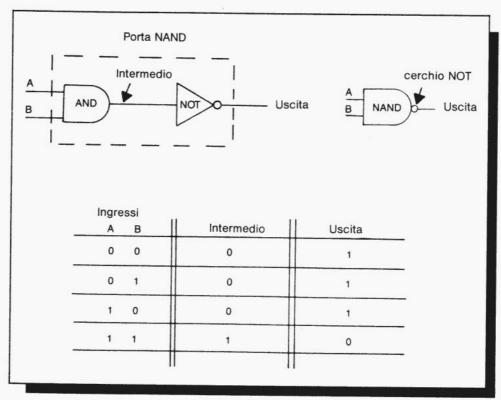

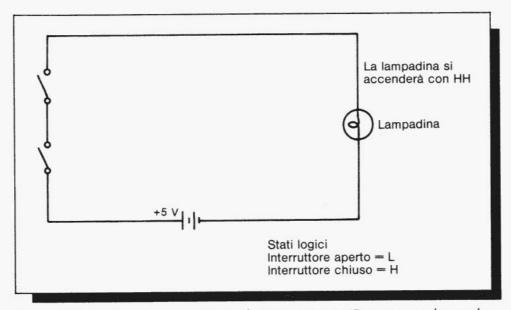

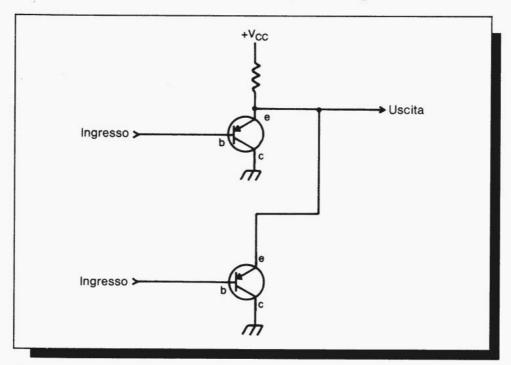

| La porta AND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 233                                    |

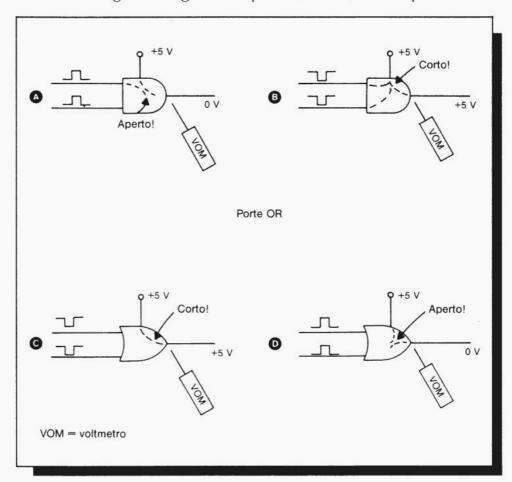

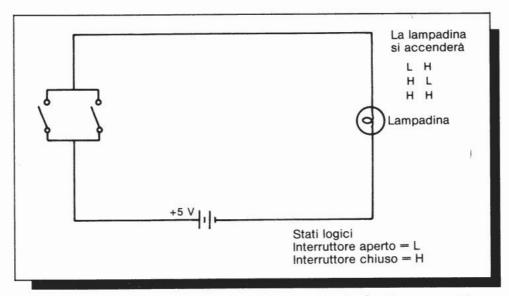

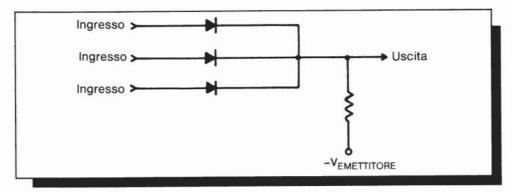

| La porta OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 237                                    |

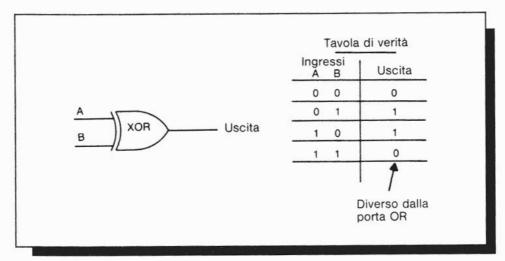

| La porta OR esclusivo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 240                                    |

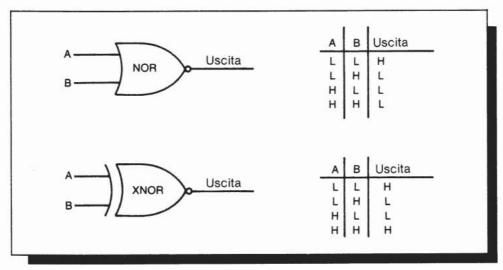

| Le porte NOR e XNOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 241                                    |

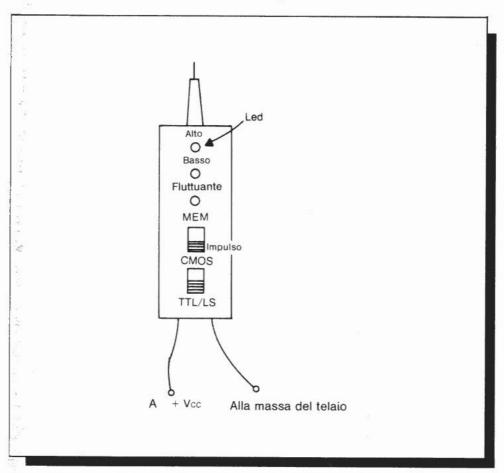

| Metodi di test delle porte logiche                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 241                                    |

| The coal at coal delice points regions with the coal at the coal a |                                        |

| Capitolo 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |

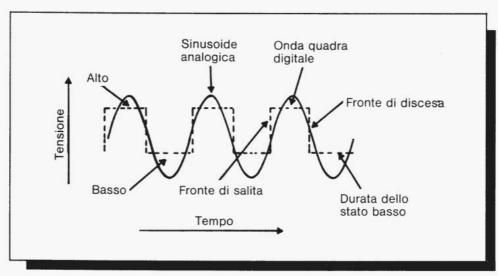

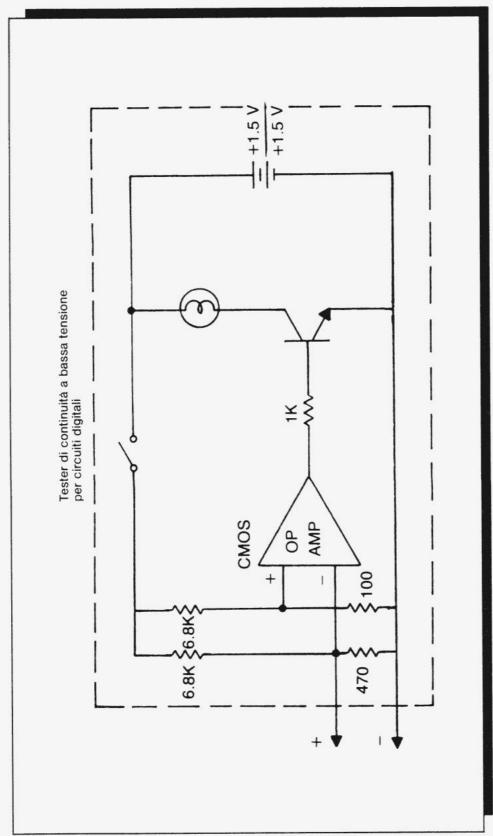

| Ricerca e riparazione dei guasti nei circuiti digitali                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 245                                    |

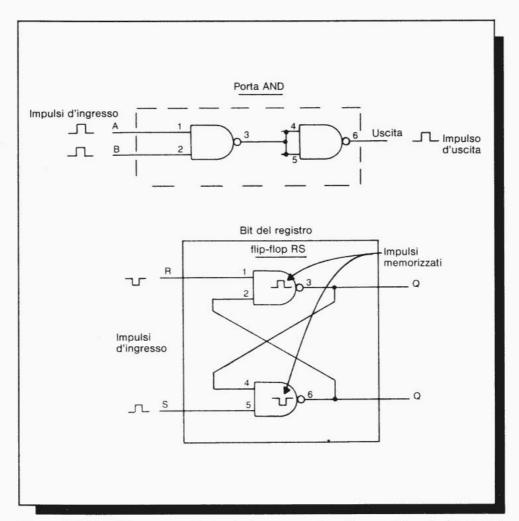

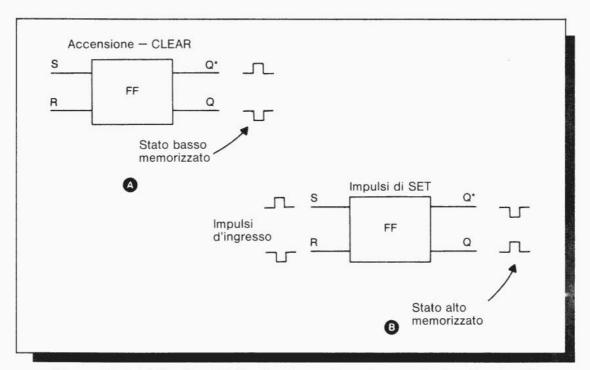

| Flip-flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 247                                    |

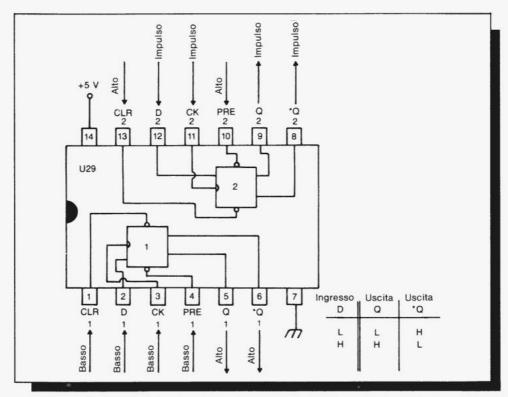

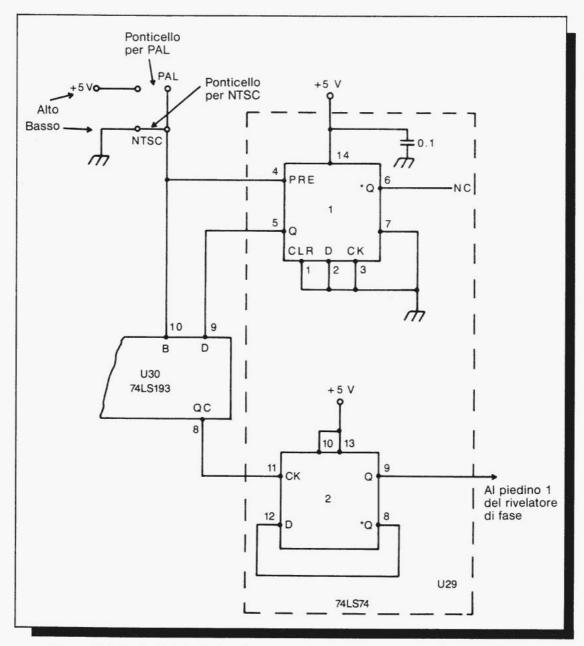

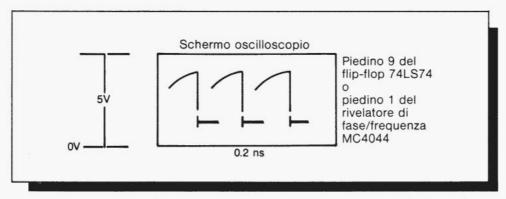

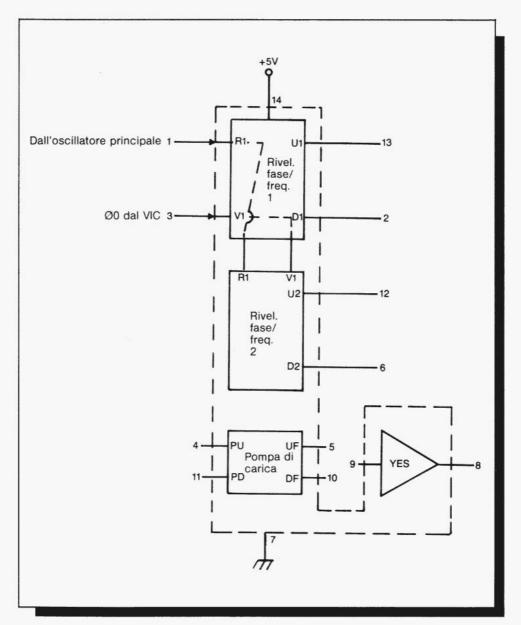

| I flip-flop di tipo D nel chip 74LS74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 249                                    |

| I latch di tipo D nel chip 74LS373                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 250                                    |

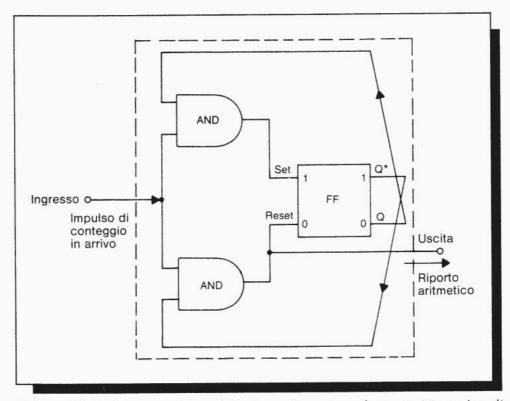

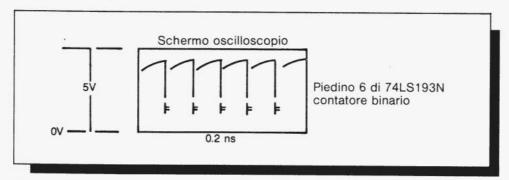

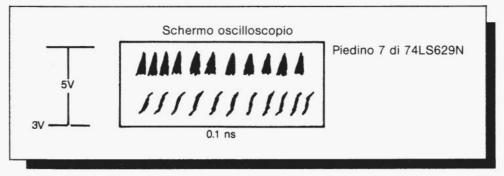

| Il contatore diretto/inverso del chip 74LS193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 252                                    |

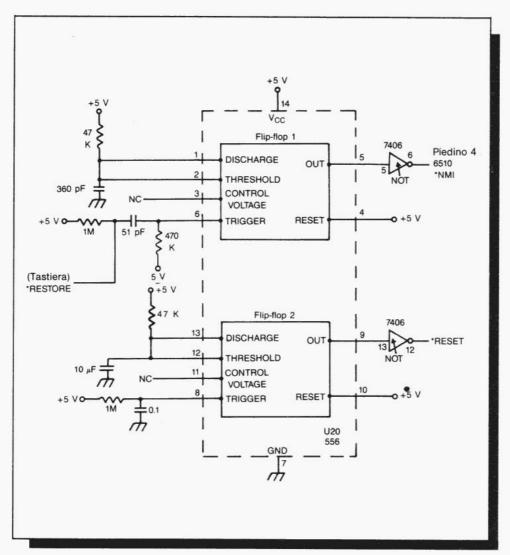

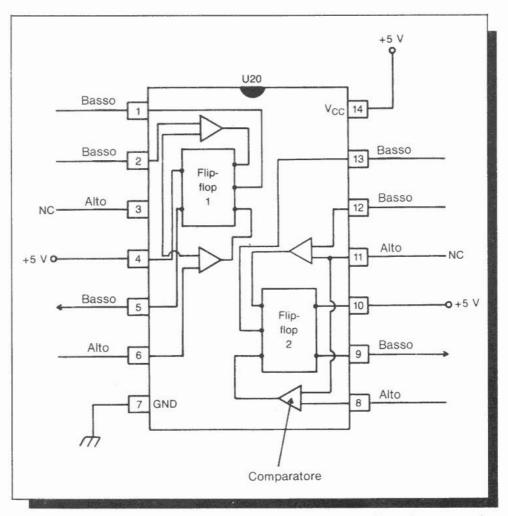

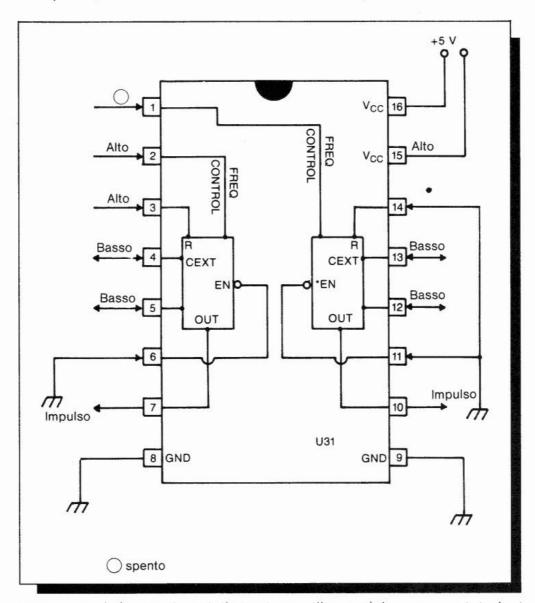

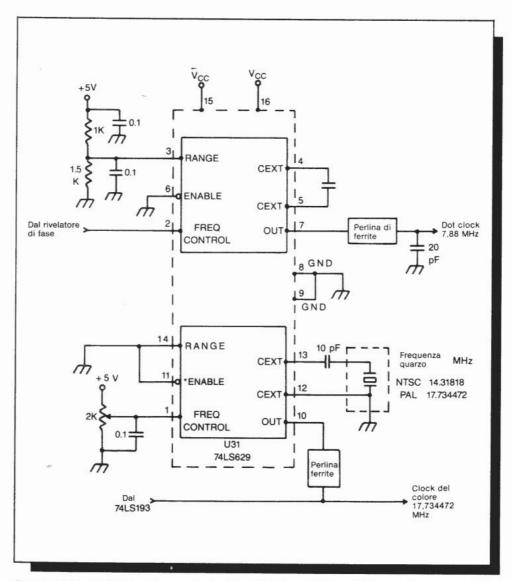

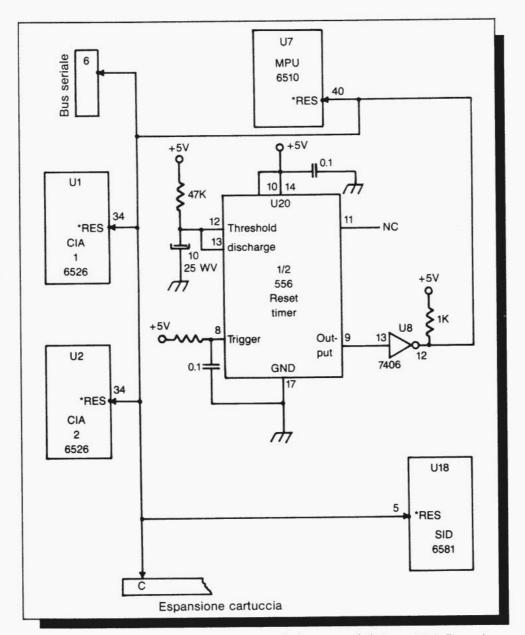

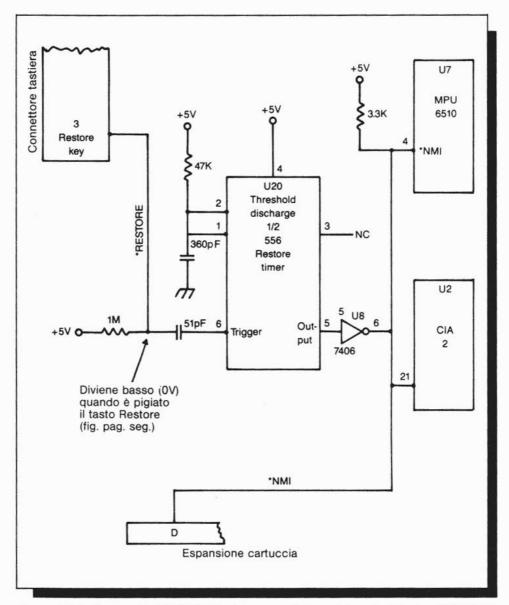

| Il timer duale del chip 556                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 257                                    |

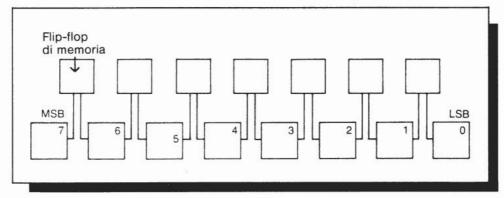

| Registri per l'elaborazione                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 259                                    |

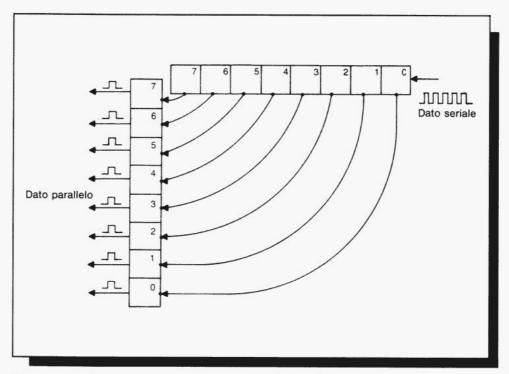

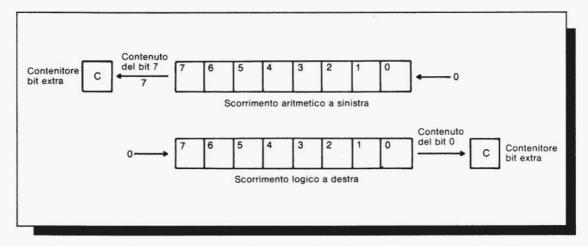

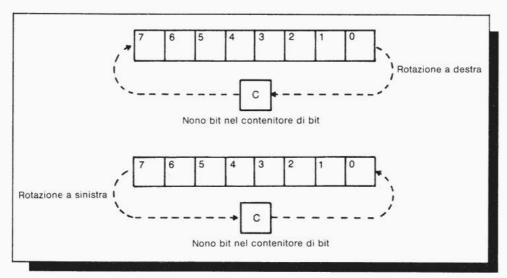

| Scorrimento                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 260                                    |

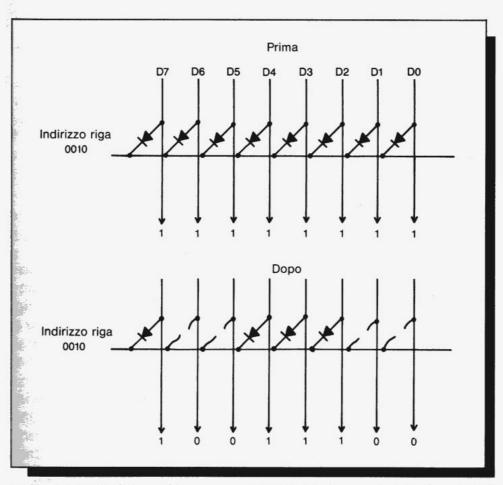

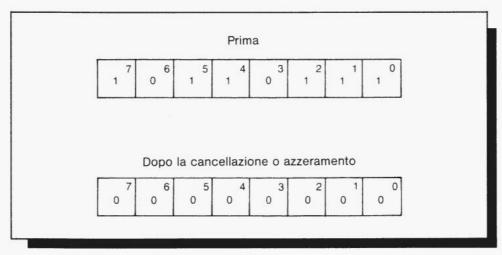

| Cancellazione, o azzeramento                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 263                                    |

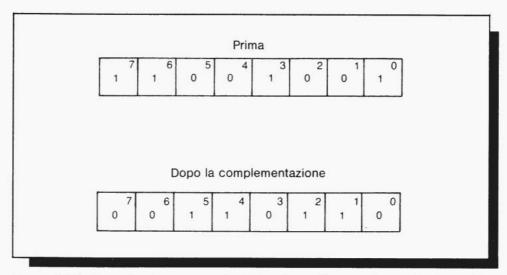

| Complementazione                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 264                                    |

| Incremento, decremento, e salto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 266                                    |

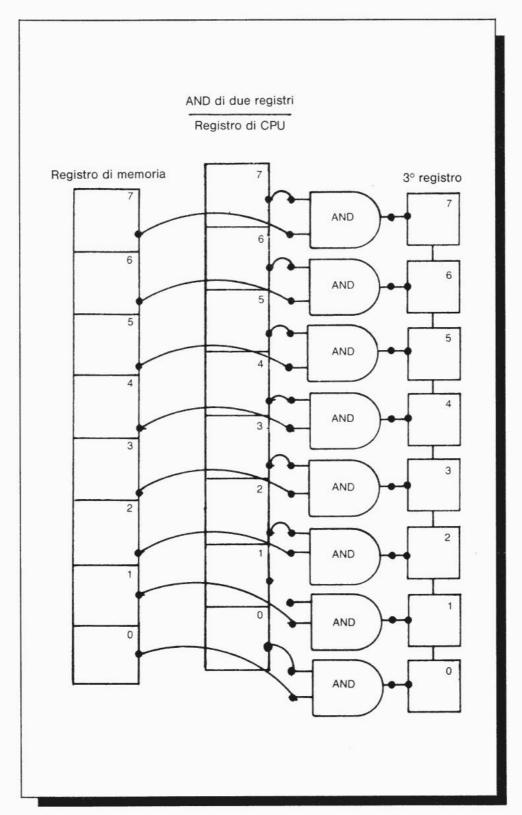

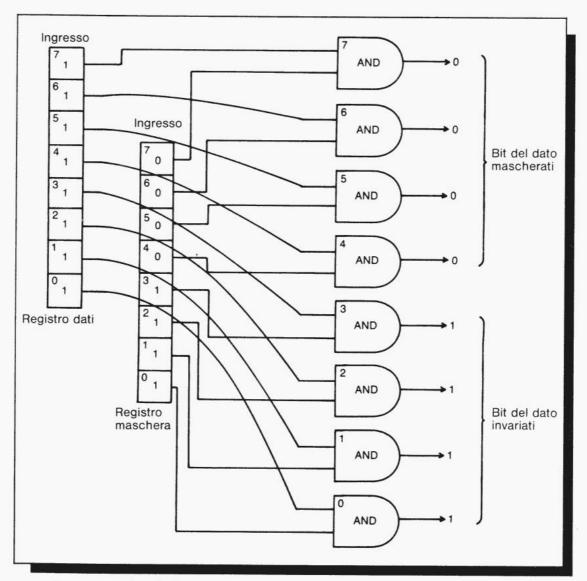

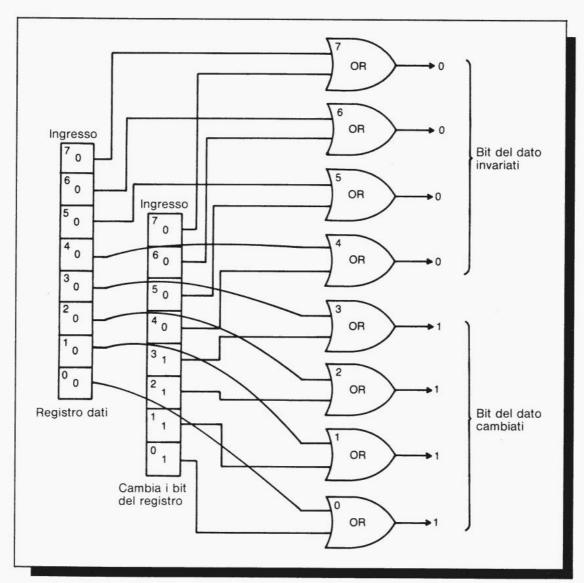

| Operazioni logiche AND e OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 268                                    |

| Cap | pitolo 12                                      |     |

|-----|------------------------------------------------|-----|

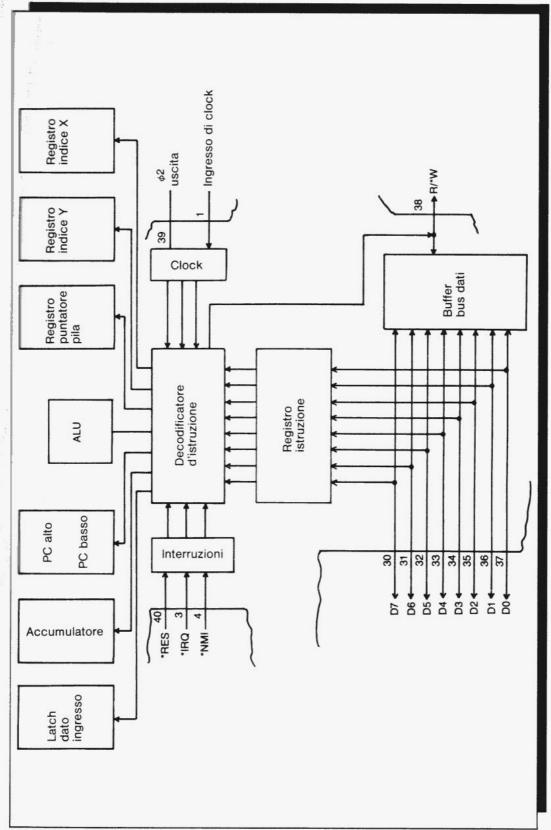

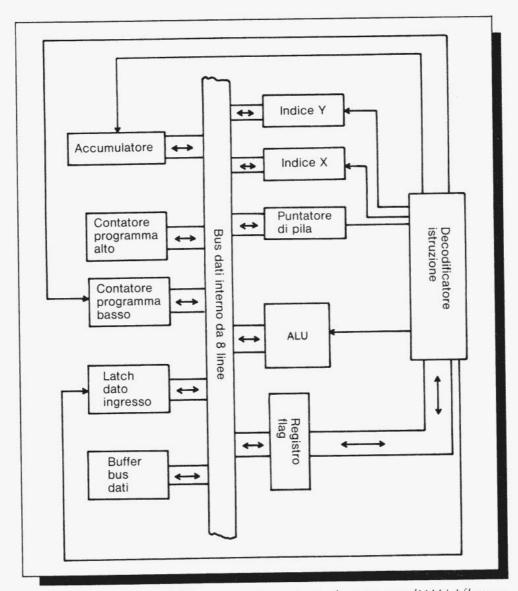

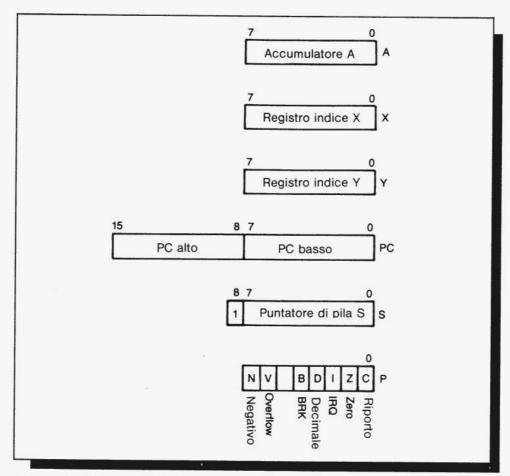

|     | Il microprocessore 6510                        | 271 |

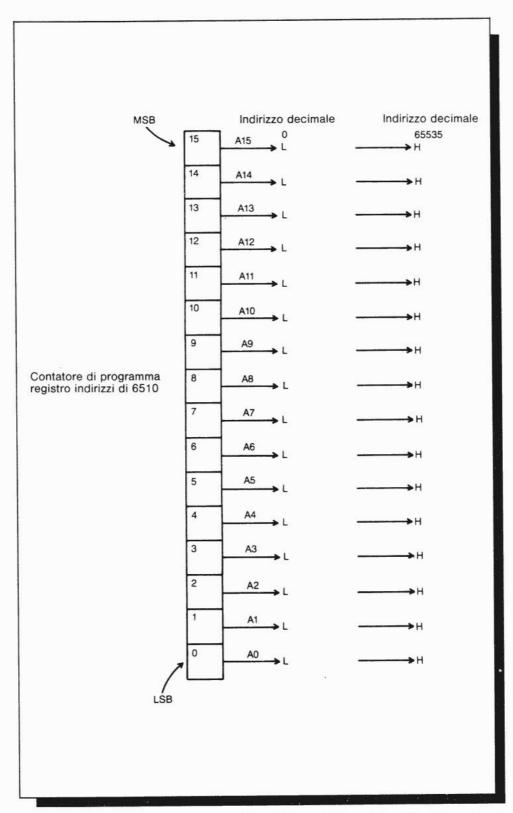

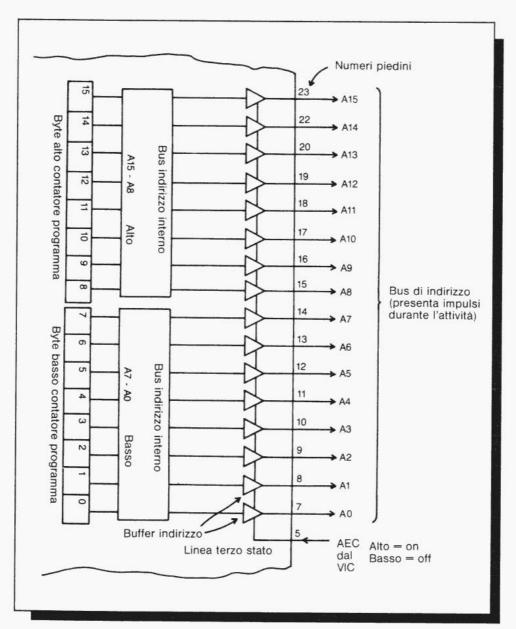

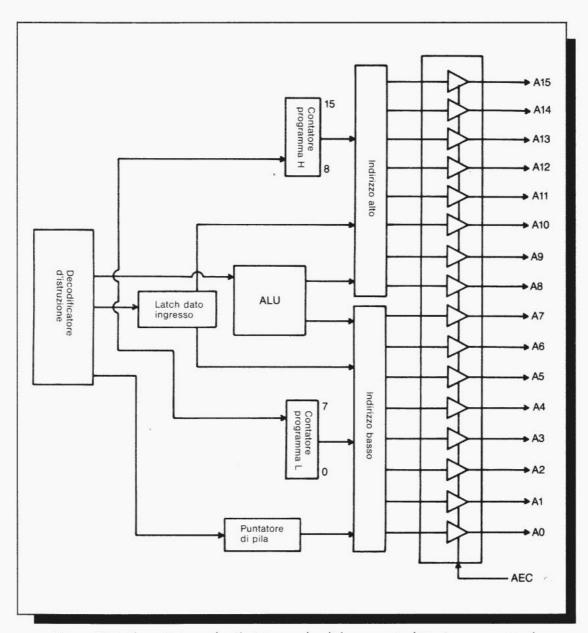

|     | Indirizzamento                                 | 272 |

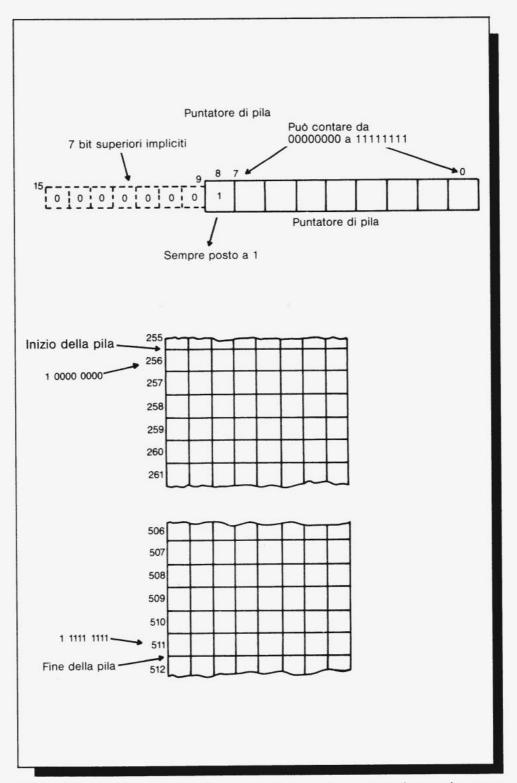

|     | La pila (stack)                                | 274 |

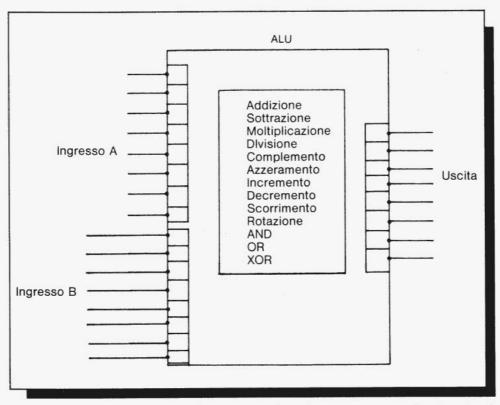

|     | L'unità aritmetico-logica                      | 277 |

|     | Scorrimento                                    | 278 |

|     | Manipolazioni logiche                          | 279 |

|     | L'accumulatore                                 | 282 |

|     | Insieme di istruzioni                          | 283 |

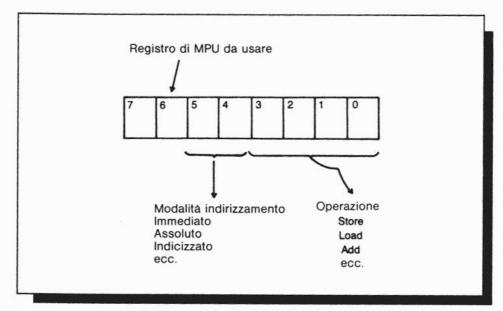

|     | Il byte dell'istruzione                        | 284 |

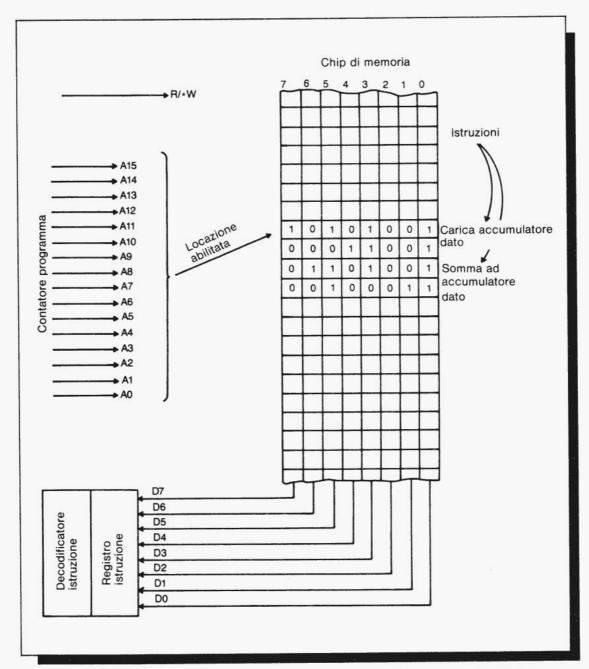

|     | Prelievo ed esecuzione                         | 285 |

|     | Registri indice                                | 289 |

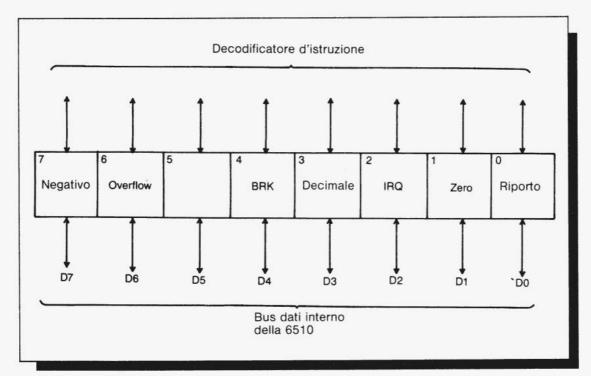

|     | Il registro di stato, o dei flag               | 289 |

|     | Interruzioni ("interrupt")                     | 294 |

|     | Indirizzi di vettori                           | 296 |

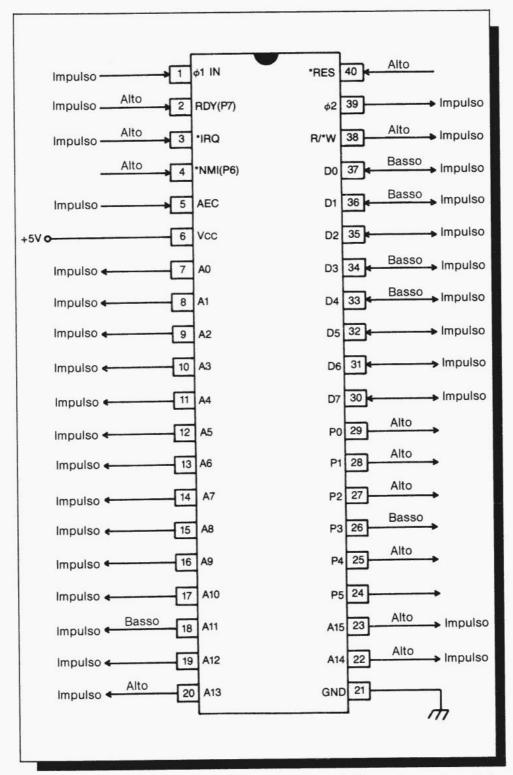

|     | Altri piedini                                  | 297 |

|     | Test                                           | 298 |

|     | lest                                           | 290 |

|     |                                                |     |

| _   |                                                |     |

| Cap | pitolo 13                                      |     |

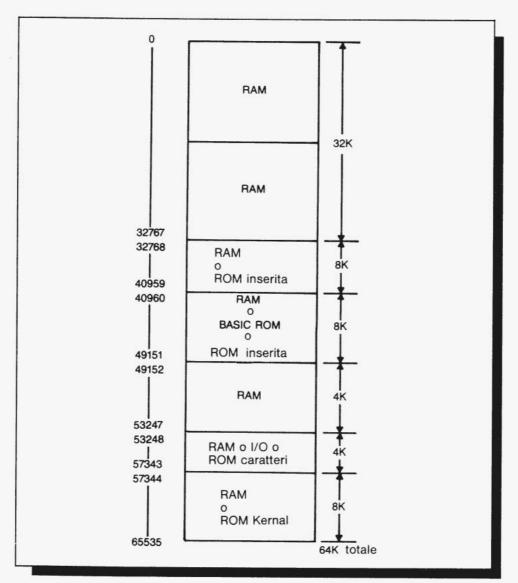

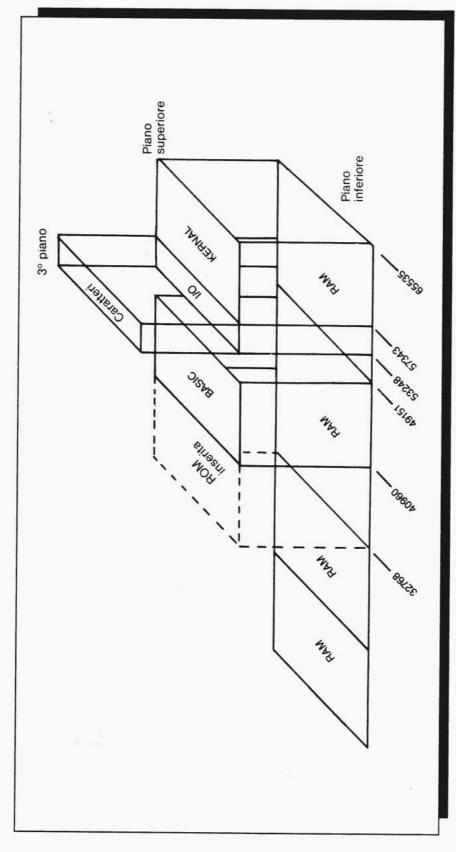

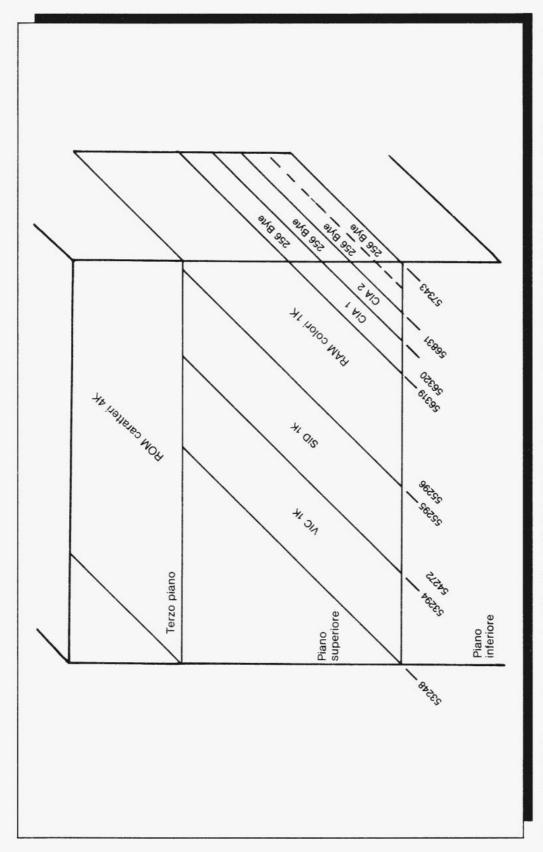

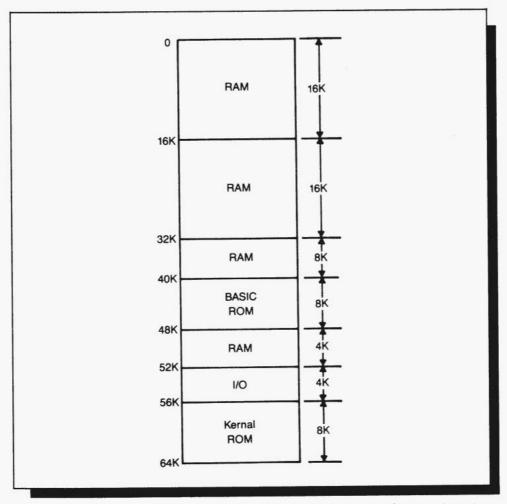

|     | Le mappe di memoria                            | 301 |

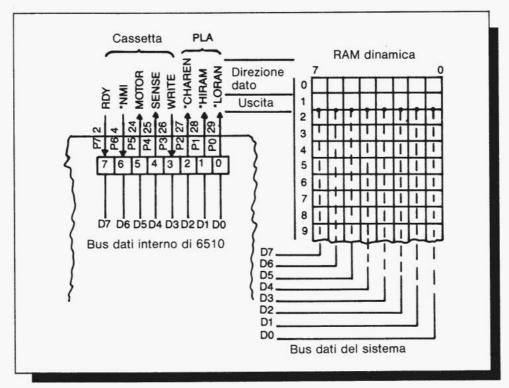

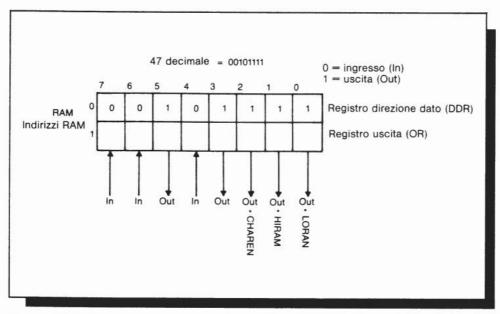

|     | La porta di I/O                                | 301 |

|     | La mappa prefissata, o di "default"            | 305 |

|     | Segnali di I/O                                 | 305 |

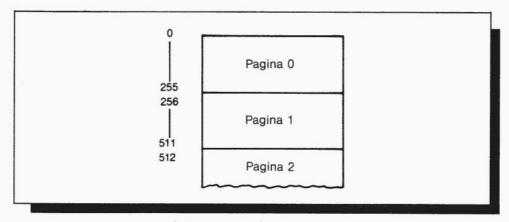

|     | Piani di mamoria                               |     |

|     | Piani di memoria                               | 307 |