# Part I FIRMWARE

# CONTENTS (FIRMWARE)

| CHAPTER 1 | GENERAL DESCRIPTIONS       | I-1           |

|-----------|----------------------------|---------------|

| 1.1       | PINE System Configuration  | I-1           |

| 1.2       | Address Map                | I <b>-</b> 5  |

| 1.3       | I/O Map                    | I-8           |

| 1.4       | Miscellaneous              | I-12          |

| CHAPTER 2 | I/O REGISTERS              | I <b>-</b> 13 |

| 2.1       | General                    | I-14          |

| 2.2       | I/O Register Descriptions  | I <b>-</b> 15 |

| 2.3       | Programming Considerations | I-34          |

| CHAPTER 3 | 7508 CPU                   | I-39          |

| 3.1       | 7508 CPU Functions         | I-40          |

| 3.2       | Interfaces                 | I-4Ø          |

| 3.3       | 7508 Commands              | I <b>-4</b> 4 |

| CHAPTER 4 | PINE INTERFACES            | I-63          |

| 4.1       | Cartridge Interface        | I-64          |

| 4.2       | Serial Interfaces          | I-73          |

| 4.3       | System Bus                 | I-8Ø          |

| 4.4       | Other Interfaces           | I-83          |

# CHAPTER 1 GENERAL DESCRIPTION

| 1.1 | 1.1.1                     | stem Configuration | I-1<br>I-1<br>I-3 |

|-----|---------------------------|--------------------|-------------------|

| 1.2 | Address                   | Map                | I-5               |

| 1.3 | I/O Map<br>1.3.1<br>1.3.2 | Introduction       | I-8<br>I-8        |

| 1.4 |                           | aneous             | I-12<br>I-12      |

#### CHAPTER 1 GENERAL DESCRIPTION

1.1 PINE System Configuration

#### 1.1.1 General

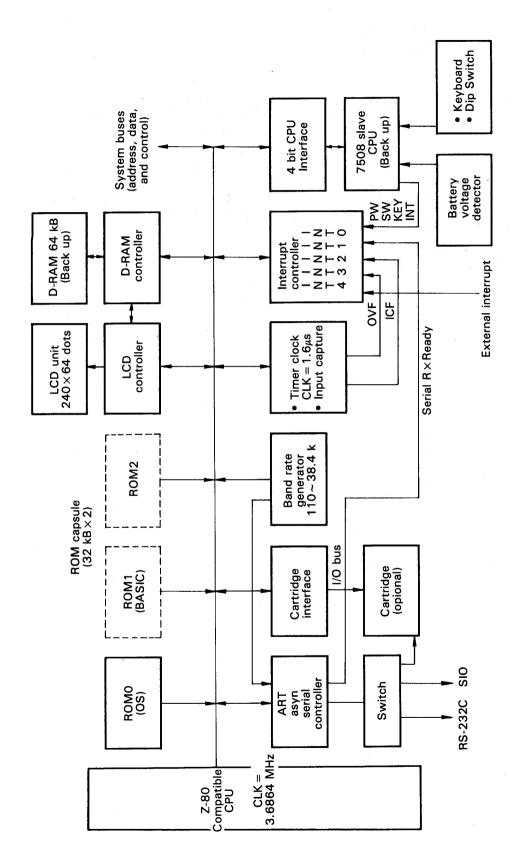

The PINE is centered on a C-MOS Z-80-compatible microprocessor. Its main memory consists of 64K bytes of RAM and up to 96K bytes of ROM. These RAM and ROM are used alternatively using a bank switching technique.

The PINE also has a 4-bit C-MOS 7508 processor, as its slave CPU, which is used to control the keyboard, clock, and power units. In addition to these processors, the PINE employs three types of semicustome gate array (GA) ICs, namely, the main memory control GA, interrupt controller GA, and I/O control GA.

Power to the PINE is supplied from the NiCd power battery, Mn dry batteries, or AC adapter.

Figure 1.1.1 shows the PINE hardware configuration.

Figure 1.1.1 Hardware Configuration

#### 1.1.2 Hardware Description

## 1.1.2.1 CPU

The PINE main CPU is a Z-80-compatible C-MOS CPU uPD70008 running at a basic clock rate of 3.6864 MHz. The CPU is put into the sleep state by the HALT instruction to save power energy.

#### 1.1.2.2 Main memory

ROM: 96K bytes (maximum): 256K-bit C-MOS mask ROM x 3 RAM: 64K bytes: 64K-bit C-MOS D-RAM x 8 Memory reads, writes, and refreshing are controlled by the D-RAM controller GA. The RAM memory is battery backed up and its data is sustained even when power switch is turned off.

#### 1.1.2.3 7508 (slave CPU)

The slave CPU is a 4-bit C-MOS 7508 microprocessor equipped with the sleep and timer functions. It runs on a basic clock of approximately 270k Hz. The 7508 is battery backed up and can continue its operation even when power is shut down. The 7508 is used to monitor the battery voltage and temperature. Its primary functions are to:

- Provide the timer/clock functions.

- Sense D-RAM temperature (at power-off time)

- Turn power on and off.

- Set and reset the system.

# 1.1.2.4 GAPNDL (Main memory control GA)

The GAPNDL controls the operations (read, write, and refresh) of the 64K-byte DRAMs as well as the 240 x 64 dots LCD unit.

# 1.1.2.5 GAPNIT (Interrupt/timer control GA)

The GAPNIT serves as:

- Interrupt controller

- Timer/baud rate generator (with input capture feature)

- Interface to the 4-bit 7508 CPU

- ROM/DRAM address decoder and DRAM address multiplexer

#### 1.1.2.6 GAPNIO (I/O control GA)

The GAPNIO serves as:

- Asynchronous Receiver Transmitter (ART)

- Centronics interface

- Cartridge (CTG) interface

- Serial I/O interface (SIO)

- RS-232C interface

- LED and buzzer interface

#### 1.1.2.7 SIO Interface

The SIO interface specifications are given below.

Level:

RS-232C level +5 V 110, 150, 200, 300, 600, 1,200, 2,400, 4,800, 9,600, 19,200, 38,400, 75 bps Baud rates

Start bits: 1 bit

1 or 2 bits Stop bits:

Parity: Even/odd or no parity

Communication mode: Full duplex

Error checking: Parity, framing, and overrun errors

The ART in the GAPNIO is used.

#### 1.1.2.8 RS-232C Interface

The RS-232C interface specifications are given below.

Level:

RS-232C level +5 V

Baud rates:

Same as for SIO. Same as for SIO.

Start bits:

Same as for SIO.

Stop bits:

Parity:

Same as for SIO.

Communication mode: Same as for SIO.

Error checking:

Same as for SIO.

The ART in the GAPNIO is used.

# 1.1.2.9 Keyboard

There are two types of keyboards for the PINE: standard and item

keyboards.

Standard keyboard:

72 keys (66 keys plus 6 switches) 58 keys (55 keys plus 3 switches)

Item keyboard:

Mechanical contacts

Contact type: Features:

N-key rollover and auto-repeat features

Programmable repeat interval

7-character buffer Stop-key only mode

#### 1.1.2.10 LCD

The PINE is provided with a 1/64-duty, 240 x 64 dot matrix LCD unit. The LCD drivers are:

**X**:

SED 1120 x 4

Y:

SED 1130 x 1

Drive voltage:

10 to 18 volts; view angle is adjustable with

a potentiometer.

VRAM area:

2K bytes

Display mode:

Dot image (no character generator)

Scrolling:

Vertical dot scrolling

#### 1.1.2.11 Buzzer

The PINE has a piezo-electric buzzer. The buzzer input is obtained by ORing the audio signal from the cartridge interface with the SP signal from the CPU. The buzzer is disconnected when an ear plug is plugged into the external loudspeaker jack.

#### 1.1.2.12 ROM capsule

The PINE can accommodate either 8K-, 16K-, or 32K-byte ROM (maskable or programmable) capsules. These ROM devices have different pin assignments as listed below.

| ROM<br>Pins | 61364 | 613128 | 613256 | 27064 | 27C256 |

|-------------|-------|--------|--------|-------|--------|

| 27pin       | 0E1*  | 0E1*   | A14    | PGM   | A14    |

| 26pin       | 0E2*  | A13    | A13    | NC    | A13    |

| 22pin       | 0E0*  | 0E0*   | 0E0    | 0E    | ŌĒ     |

| 20pin       | CS*   | CS*    | CS*    | CS    | CS     |

Asterisks identify mask-programmable ROMs.

P-ROM -Maskable-

OEØ\* and CS\* must be active low. For 61364, \*E1\* must be active high and \*E2\* must be active low. For 613128, OE1\* is don't care or must be active low. When OEl\* is set to active low, jumper J4 or J5 to side B.

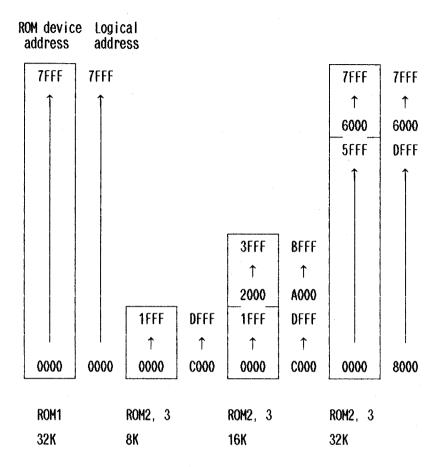

#### 1.2 Address Map

The PINE has four types of memory:

- 1) DRAM (64K bytes)

- ROM1

- 3) ROM2

- 4) ROM3

- 5) External memory

DRAMs make up a 46K bytes of system RAM memory and are controlled by gate array GAPNDL. ROM1 is used to store the operating system and ROM2 and ROM3 to store application programs. Both have a maximum capacity of 32K bytes (may also be used as 16K- or 8K-byte ROM). The external memory refers to the memory which is installed in the external expansion box and connected to the main unit through the system bus. The main unit does not know whether it is made up of ROM or RAM devices.

A 4-bit bank switch (BANKR bits 7-4 for BANKØ through BANK3) is provided for memory management. This switch is used in conjunction with the address inputs to address the memory. Figure 1.2.1 shows the relationship between BANK3 through BANKØ and their address spaces.

The memory devices installed in the main unit are all controlled by gate array GAPNIT. GAPNIT issues a Select (enable) signal to the memory in the main unit when  $\overline{\text{MEN}}$  from the external expansion box is  $\emptyset$  and disables the main unit memory when  $\overline{\text{MEN}}$  is 1.

MEN is held at the Ø level when no external expansion box is installed. If an external expansion box is installed, all memory is controlled by the external expansion box.

The external expansion box a bank signal for memory management (different from those generated by GAPNIT and assigned a 1-level higher priority) which is used with the address inputs to determine whether the main unit memory or external memory is to be used.

When using the main unit memory, the external expansion box sets  $\overline{\text{MEN}}$  to  $\emptyset$  to disable the external memory and leaves the main memory addressing to GAPNIT's control. When using the external memory, it sets  $\overline{\text{MEN}}$  high to disable the memory in the main unit. The GAPNIT does nothing for external memory addressing.

| Bank         | 0    | 1    |      | 2    |           |      | 3    |        |             |

|--------------|------|------|------|------|-----------|------|------|--------|-------------|

| ROH          |      |      | 8K   | 16K  | 32K       | 8K   | 16K  | 32K    |             |

| Code         | 0000 | 0100 | 1000 | 1001 | 1010      | 1100 | 1101 | 1110 - | <b>}</b>    |

| FFFF<br>E000 |      | E    | RAM  | RAM  | RAM       | RAM  | RAM  | RAM    | (BAN<br>321 |

| C000_        | RAM  | С    | ROM2 | ROM2 | ROM2<br>C | ROM3 | ROM3 | ROM3   |             |

| A000_        |      | ,    | A    |      |           | A    |      |        |             |

| _8000        |      | RAM  |      |      |           | -    |      |        |             |

| 6000_        |      |      |      | 6    |           |      | 6    |        |             |

| 4000_        | ROM1 |      | RAM  | RAM  | RAM       | RAM  | RAM  | RAM    |             |

| 2000_        | (08) |      |      |      |           |      |      |        |             |

| 0000         |      |      | !    |      |           |      |      |        |             |

Fig. 1.2.1 PINE Memory Map

Note: Note the relationship between the logical and physical ROM addresses when programming ROM devices.

\* See also the figure on the previous page.

#### 1.3 I/O Map

#### 1.3.1 Introduction

The PINE I/O addresses space is allocated to the three gate array LSIs (i.e., GAPNIT, GAPNDL, and GPNIO) and the I/O devices in the external expansion box. The GAPNIT are assigned I/O addresses P00H through P07H, the GAPNDL is assigned P08H through P0FH, the GAPNIO is assigned P10H through P1FH, and the external I/O devices P20H through PFFH.

#### 1.3.2 I/O Address Space

Table 1.3.1 lists the I/O addresses assigned to the PINE. In the table, I/O address bits identified by an asterisk (EDJ and ECA) are used only for development boards and valid only for board development. The unused I/O addresses between P00H through P1FH must not be used by the user. Any accesses to inhibited I/O address may cause computer malfunctions.

Details about the I/O registers are found in Chapter 2, "I/O Registers."

| I/0<br>Adderss | Read (bit)                                  | Write (bit)                                   | Device |

|----------------|---------------------------------------------|-----------------------------------------------|--------|

| 1/0<br>Add     | 7 6 5 4 3 2 1 0                             | 7 6 5 4 3 2 1 0                               |        |

| 00             | ICRL · C ICR · Low command trigger (8)      | CTLR1 control register 1 (8)                  |        |

|                | 8 bits data                                 | BRG3 BRG2 BRG1 BRG0 SWBCR BCR1 BCR0 SLBCR     |        |

| 01             | ICRH • C ICR • High command trigger (8)     | CMDR command register (3)                     |        |

| U1             | 8 bits data                                 | RESET RESET SET OVER ROYSIO ROYSIO            |        |

| 02             | ICRL • B ICR • Low barcode trigger (8)      | CTLR2 control register (2)                    |        |

|                | 8 bits data                                 | RMT MIC                                       |        |

| 03             | ICRH · B ICR · High barcode trigger (8)     |                                               | _      |

| VS             | 8 bits data                                 |                                               | -      |

| 04             | ISR interrupt status register (5)           | IER interrupt enable register (5)             | GAPN   |

| V4             | EXT OVF LCF RXRDY 7508                      | EXT OVF ICF RXRDY 7508                        | g,     |

| 05             | STR status register (8)                     | BANKR bank register (8)                       |        |

| Vo             | BANK3 BANK2 BANK1 BANK0 RDYSIO RDY BCRD EAR | BANK3 BANK2 BANK1 BANKO *EDU *ECA CKS#1 CKS#0 |        |

| 06             | SIOR serial IO register (8)                 | SIOR serial IO register (8)                   |        |

| 00             | 8 bits data                                 | 8 bits data                                   |        |

| 07             |                                             |                                               |        |

|                |                                             |                                               |        |

| 08             |                                             | VADR VRAM start address register (5)          |        |

|                |                                             | A15 A14 A13 A12 A11                           | _      |

| 09             |                                             | YOFF Y offset register (7)                    | GAPND  |

|                |                                             | DSP Y5 Y4 Y3 Y2 Y1 Y0                         | AP     |

| 0A             |                                             | FR frame register (4)                         | 9      |

| J.,            |                                             | F3 F2 F1 F0                                   |        |

1.3.1 (1)

| I/0<br>Adderss | Read (bit) 7 6 5 4 3 2 1 0                                          | Write (bit) Device 7 6 5 4 3 2 1 0              |

|----------------|---------------------------------------------------------------------|-------------------------------------------------|

| ОВ             |                                                                     | SPUR speed-up register (6)                      |

| 00             |                                                                     | PRE2 PRE1 PRE0 POST2 POST1 POST0                |

| oc             |                                                                     | DL                                              |

| 00             |                                                                     | GAPND                                           |

| 0E             |                                                                     |                                                 |

| 0F             |                                                                     |                                                 |

| 10             |                                                                     |                                                 |

| 11             | CTG IF<br>(cartridge interface)                                     | CTG IF<br>(cartridge interface)                 |

| 12             | address space                                                       | address space                                   |

| 13             |                                                                     | GAPN                                            |

| 14             | ARTDIR ART data input register (8) 7/8 bits data                    |                                                 |

| 15             | ARTSR ART status register (7)  RDSR FE OE PE TX RX TX empty RDY RDY | ARTMR ART mode register (4)  STOP EVEN PEN DATA |

1. 3. 1 (2)

| I/0<br>Adderss | 7    | 6     | 5        | Read  | 3      | 2        | 1        | bit)     | 7         |         | <u> </u> |            | Wri        |           | (l   | oit) | Device |

|----------------|------|-------|----------|-------|--------|----------|----------|----------|-----------|---------|----------|------------|------------|-----------|------|------|--------|

|                |      |       | <u></u>  |       | regis  | <u> </u> | <u> </u> | <u> </u> | 7<br>ARTI |         | <u> </u> | 4<br>mmana | 3<br>1 rea | 2<br>iste |      | (6)  |        |

| 16             | CAUD | CSEL  | <u> </u> |       | RXD    | SIN      | PERR     | T        |           |         | RRTS     | ER         | SBRK       |           | RDTR | TxE  |        |

| 17             |      |       |          |       |        |          |          |          | PDR       | pl      | rinte    | r da       | ta re      | gist      | er   | (8)  |        |

|                |      |       |          | ę.    |        | <u></u>  |          |          |           |         | 3 bit    | ts da      | ata        |           |      |      |        |

| 18             |      |       |          |       | _      |          |          |          | SWR       | SI      | witch    | reg        | ister      | <b>.</b>  | T    | (5)  |        |

|                |      |       |          |       |        | <u> </u> | _        | <u></u>  |           | <u></u> |          | AUSW       | SSW1       | SSWO      | CSW1 | CSNO |        |

| 19             |      | _     |          |       |        |          |          |          | IOC       | TLR 1   | [0 co    | ntro       | reg        | iste      | •    | (8)  |        |

|                |      |       |          |       |        | _        | <u></u>  | _        | SP        | LED2    | LED1     | LED0       | CRS        | SOUT      | PINI | PSTB |        |

| 1A             |      |       |          |       |        |          |          | _        |           |         | _        |            |            | _         |      |      | OIN    |

| 1B             |      |       |          |       | _      |          |          |          |           |         |          |            |            |           |      |      | GAPNI  |

| 10             |      |       |          |       |        |          |          |          |           |         |          |            |            |           |      |      |        |

| 1D             |      |       |          |       |        |          |          |          |           | _       |          |            |            |           |      |      |        |

| 1E             |      |       |          |       |        |          |          |          |           |         |          |            |            |           |      |      |        |

| 1F             |      |       |          |       |        |          |          |          |           |         |          |            |            |           |      |      | 4      |

| 20             | F    | Reser | ved f    | or th | ne I/C | ) dev    | ices     | in th    | e ext     | erna    | ıl exi   | pansi      | on b       | 0X.       |      |      |        |

1. 3. 1 (3)

#### 1.4 Miscellaneous

### 1.4.1 Z-80 Wait Operation

The PINE uses part of the DRAM address space as a video RAM area. Since the M1 cycle is too short to successfully access the VRAM area, the PINE Z-80 CPU inserts one wait state into every M1 cycle. This means that one wait state is inserted into every M1 cycle while an application program is being executed in DRAM. No wait state is insert when a program on ROM is executed and no DRAM is accessed. It follows from this discussion that the same program executes at different execution speeds when it is executed in DRAM and when it is implemented on ROM.

# CHAPTER 2 I/O REGISTERS

| 2.1 | Genera] | L                          | I <b>-</b> 14 |

|-----|---------|----------------------------|---------------|

| 2.2 | I/O Rec | gister Description         | I <b>-</b> 15 |

|     | 2.2.1   | PØØH: ICRL.C               | I-15          |

|     | 2.2.2   | PØØH: CTLR1                | I-16          |

|     | 2.2.3   | PØ1H: ICRH.C               | I-18          |

|     | 2.2.4   | PØ1H: CMDR                 | I-19          |

|     | 2.2.5   | PØ2H: ICRL.B               | I-19          |

|     | 2.2.6   | PØ2H: CTLR2                | I-19          |

|     | 2.2.7   | PØ3H: ICRH.B               | I-20          |

|     | 2.2.8   | PØ4H: ISR                  | I-20          |

|     | 2.2.9   | PØ4H: IER                  |               |

|     | 2.2.10  | PØ5H: STR                  | 1-22          |

|     | 2.2.11  | PØ5H: BANKR                | I -23         |

|     | 2.2.12  | PØ6H: SIOR                 | I-23<br>I-24  |

|     | 2.2.13  | PØ8H: VADR                 | I-24          |

|     | 2.2.14  | PØ9H: YOFF                 | 1-25          |

|     | 2.2.15  | PØAH: FR                   | I-25          |

|     | 2.2.16  | PØBH: SPUR                 | I-20          |

|     | 2.2.17  | PlØH-Pl3H                  | I-27          |

|     | 2.2.18  | P14H: ARTDIR               | I-28          |

|     | 2.2.19  | P14H: ARTDOR               |               |

|     | 2.2.20  | P15H: ARTSR                | I-28          |

|     | 2.2.21  | P15H: ARTMR                | I-29<br>I-30  |

|     | 2.2.22  | P16H: IOSTR                |               |

|     | 2.2.23  | Pl6H: ARTCR                | I-31          |

|     | 2.2.24  | P17H: PDR                  | I-32          |

|     | 2.2.25  | P18H: SWR                  | I-33          |

|     | 2.2.26  | P19H: IOCTLR               | I-33          |

|     | 2.2.27  | P2ØH-PFFH                  | I-35          |

|     | 2.2.21  | rzwn-rrrn                  | I-35          |

| 2.3 | Program | ming Considerations        | I-36          |

|     |         | Initial I/O Register Reset | I-36          |

|     | 2 3 2   | Writing to an I/O Dort     | T 20          |

#### CHAPTER 2 I/O REGISTERS

This chapter describes the I/O registers, their usage, and their relationship to the PINE operating system.

#### 2.1 General

The PINE I/O registers are located in I/O port addresses P00H through PFFH. I/O addresses P00H through PIFH are for the internal I/O devices and P20H through PFFH for the external I/O devices.

The optional external RAM disk unit uses I/O addresses P90H through P94H. I/O address P94H is used in the read mode to check the presence or absence of the external RAM disk so it is not available to the user when an external device is used (through the system bus).

Since the output state of some I/O registers is maintained by the operating system, the user program must rewrite the corresponding system RAM areas when rewriting such I/O registers. (See Section 2.3, "Programming Considerations").

## 2.2 I/O Register Descriptions

# 2.2.1 P00H: ICRL.C (Input Capture Register Low Command Trigger) (read mode)

| Bit | Name  | Description                        |

|-----|-------|------------------------------------|

| 7   | ICR 7 |                                    |

| 6   | ICR 6 |                                    |

| 5   | ICR 5 |                                    |

| 4   | ICR 4 | Input capture register lower order |

| 3   | ICR 3 | 8 bits                             |

| 2   | ICR 2 |                                    |

| 1   | ICR 1 | ,                                  |

| 0   | ICR 0 | ]                                  |

#### Explanation:

P00H is assigned to the lower 8 bits of the input capture register. The contents (both higher and lower order bytes) of the FRC (Free Running Counter) are latched into the ICR (Input Capture Register) immediately when this register is read. The higher order value can be obtained by reading I/O address P01H (ICRHC).

P00H is used to read the contents of the FRC.

# 2.2.2 PØØH: CTLR1 (Control Register 1) (write mode)

|     | Υ          |                                                                    |  |  |  |  |  |  |  |  |

|-----|------------|--------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Bit | Name       | Description                                                        |  |  |  |  |  |  |  |  |

| 7   | BRG 3      |                                                                    |  |  |  |  |  |  |  |  |

| 6   | BRG 2      |                                                                    |  |  |  |  |  |  |  |  |

| 5   | BRG 1      | Band Rate Generator Select                                         |  |  |  |  |  |  |  |  |

| 4   | BRG O      |                                                                    |  |  |  |  |  |  |  |  |

| 3   | SWBCR      | Power switch for +5vdc power to the barcode reader = 1 : Power on  |  |  |  |  |  |  |  |  |

|     |            | =O :Power off                                                      |  |  |  |  |  |  |  |  |

| 2   | BCR1 (up)  | } Barcode mode select                                              |  |  |  |  |  |  |  |  |

| 1   | BCRO(down) | S par code mode serect                                             |  |  |  |  |  |  |  |  |

| 0   | SLBCR      | Selects the trigger signal for latching the FRC data into the FRC. |  |  |  |  |  |  |  |  |

|     |            | = 1 : Barcode reader input                                         |  |  |  |  |  |  |  |  |

|     |            | =0: External cassette ear input                                    |  |  |  |  |  |  |  |  |

#### Explanation:

BRG3-BRGØ specify the baud rate for the serial interface and BCR1 and BCR2 specify the polarity of the ICR trigger.

# Band Rate Generator Select

| E | 3 | R | G |   | Τ      | rans | mit      |    | Receive |      |          |    |

|---|---|---|---|---|--------|------|----------|----|---------|------|----------|----|

| 3 | 2 |   | 1 | 0 | T×C    |      | Baud rat | te | R×C     |      | Baud rat | te |

| 0 | 0 | ( | ) | 0 | 1.7454 | 5 k  | 110      |    | 1.7454  | 15 k | 110      |    |

| 0 | 0 |   | ) | 1 | 2.4    | k    | 150      |    | 2.4     | k    | 150      |    |

| 0 | 0 | ŀ | 1 | 0 | 4.8    | k    | 300      |    | 4.8     | k    | 300      |    |

| 0 | 0 | 1 | 1 | 1 | 9.6    | k    | 600      |    | 9.6     | k    | 600      |    |

| 0 | 1 |   | 0 | 0 | 19.2   | k    | 1.2      | k  | 19.2    | k    | 1.2      | k  |

| 0 | 1 |   | ) | 1 | 38.4   | k    | 2.4      | k  | 38.4.   | k    | 2.4      | k  |

| 0 | 1 |   | 1 | 0 | 76.8   | k    | 4.8      | k  | 76.8    | k    | 4.8      | k  |

| 0 | 1 | ŀ | 1 | 1 | 153.6  | k    | 9.6      | k  | 153.6   | k    | 9.6      | k  |

| 1 | 0 |   | 0 | 0 | 19.2   | k    | 1.2      | k  | 1.2     | k    | 75       |    |

| 1 | 0 |   | 0 | 1 | 1.2    | k    | 75       |    | 19.2    | k    | 1.2      | k  |

| 1 | 0 | 1 | 1 | 0 | 307.2  | k    | 19.2     | k  | 307.2   | k    | 19.2     | k  |

| 1 | 0 | 1 | 1 | 1 | 614.4  | k    | 38.4     | k  | 614.4   | k    | 38.4     | k  |

| 1 | 1 |   | 0 | 0 | 3.2    | k    | 200      |    | 3.2     | k    | 200      |    |

# Barcode mode select settings

| BCR1 | BCRO |            | Trigger polarity             |

|------|------|------------|------------------------------|

| 0    | 0    |            | Trigger inhibit              |

| 0    | 1    |            | Falling-edge trigger         |

| 0    | 1    | <u>J</u> L | Rising-edge trigger          |

| 0    | 1    | <u>I</u>   | Rising-/falling-edge trigger |

Programming note:

The PINE OS stores the write data to the CTLRl in system RAM area RZCTLRl (ØFØØlH) for use during update processing. When writing the CTLRl directly from a user program, therefore, it is necessary to rewrite the contents of the RZCTLRl simultaneously. The bit format of the RZCTLRl is identical to that of the CTLRl.

Example: Turning on barcode power

LD A, (RZCTLR1)

OR Ø8H

LD (RZCTLR1), A

OUT (CTLR1), A

The OS also updates the baud rate setting through BIOS RSIOX or during accesses to the FDD.

# 2.2.3 P01H: ICRH.C (Input Capture Register High Command Trigger) (read mode)

| Bit: | Name   | Description                         |

|------|--------|-------------------------------------|

| 7    | ICR 15 |                                     |

| 6    | ICR 14 | <b>-</b>                            |

| 5    | ICR 13 | 7                                   |

| 4    | ICR 12 | Input capture register higher order |

| 3    | ICR 11 | 8 bits                              |

| 2    | ICR 10 | <b>1</b>                            |

| 1    | ICR 9  | 7                                   |

| 0    | ICR 8  | ] ]                                 |

Explanation:

PØ1H is read to fetch the contents of the FRC. Bits ICR15-ICR8 are latched immediately when the ICRLC (PØ0H) is read. Accordingly, the ICRLC must be read before the ICRHC is read.

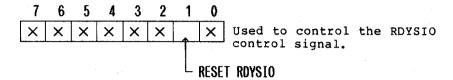

#### 2.2.4 PØ1H: CMDR (Command Register) (write mode)

| Bit                   | Name       | Description                                                                                                            |

|-----------------------|------------|------------------------------------------------------------------------------------------------------------------------|

| 7<br>6<br>5<br>4<br>3 |            | } Ignored                                                                                                              |

| 2                     | RES OVF    | =1: Resets the INTR signal set by an FRC overflow interrupt. =0: Does nothing.                                         |

| 1                     | RES RDYSIO | =1: Resets the RDYSIO signal (indicating the 7508ready state). =0: Does nothing.                                       |

| 0                     | SET RDYSIO | =1: Sets the RDYSIO signal used for communication with the 7508.  =0: Does nothing.  This bit is used only the system. |

Programming note:

The PINE OS uses the RES OVF bit during OVF interrupt processing and the RES RDYSIO bit during communication with the 7508.

2.2.5 P02H: ICRL.B (Input Capture Register Low Barcode Trigger) (read mode)

| Bit | Name  | Description                                                                                                       |

|-----|-------|-------------------------------------------------------------------------------------------------------------------|

| 7   | ICR 7 |                                                                                                                   |

| 6   | ICR 6 |                                                                                                                   |

| 5   | ICR 5 |                                                                                                                   |

| 4   | ICR 4 | Input capture register lower order 8 bits set by the state transition of the barcode or external cassette signal. |

| 3   | ICR 3 |                                                                                                                   |

| 2   | ICR 2 |                                                                                                                   |

| 1   | ICR 1 |                                                                                                                   |

| 0   | ICR 0 |                                                                                                                   |

Explanation:

PØ2H is assigned to the lower 8 bits of the ICR which are loaded with data from the FRC on the negative-to-positive or positive-to-negative transition of the barcode (BCRD) or external cassette (EAR) signal. The transition of the BCRD or EAR signal is identified by the INT2 signal (ICF) being made active. Either barcode reader or external cassette is selected by the CTLR1, bit SWBCR.

#### 2.2.6 PØ2H: CTLR2 (Control Register) (write mode)

| Bit                        | Name | Description                                                                                                        |

|----------------------------|------|--------------------------------------------------------------------------------------------------------------------|

| 7<br>6<br>5<br>4<br>3<br>2 |      | } Ignored                                                                                                          |

| 1                          | RMT  | Turns on or off the external cassette remote mode.ready state). =1:Turns on remote mode. =0:Turns off remote mode. |

| 0                          | MIC  | Write signal (MIC output) to the external cassettedrive.                                                           |

#### Explanation:

P02H is used to control the RMT and MIC lines of the external cassette interface.

#### Programming note:

The PINE OS does not support the external cassette. It is supported only by BASIC.

# 2.2.7 PØ3H: ICRH.B (Input Capture Register High Barcode Trigger) (read mode)

| Bit | Name   | Description                                                                                                        |

|-----|--------|--------------------------------------------------------------------------------------------------------------------|

| 7   | ICR 15 |                                                                                                                    |

| 6   | ICR 14 |                                                                                                                    |

| 5   | ICR 13 |                                                                                                                    |

| 4   | ICR 12 | Input capture register higher order 8 bits set by the state transition of the barcode or external cassette signal. |

| 3   | ICR 11 |                                                                                                                    |

| 2   | ICR 10 |                                                                                                                    |

| 1   | ICR 9  |                                                                                                                    |

| 0   | ICR 8  |                                                                                                                    |

#### Explanation:

P02H is assigned to the higher 8 bits of the ICR which are loaded with data from the FRC on the negative-to-positive or positive-to-negative transition of the barcode (BCRD) or external cassette (EAR) signal. Reading this register resets the INT2 signal (ICF) that is made active by the transition of the BCRD or EAR.

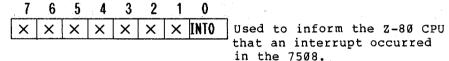

# 2.2.8 P04H: ISR (Interrupt Status Register) (read mode)

| Bit         | Name        | Description                                                                                                                                                                                                                                                              |

|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>6<br>5 |             | Always set to 0.                                                                                                                                                                                                                                                         |

| 4           | INT4(EXT)   | External interrupt signal. Reset by returning aresponse signal to the external expansion box.                                                                                                                                                                            |

| 3           | INT3 (OVF)  | Interrupt signal set when an FRC overflow condition occurs. Reset by setting the CMDR (PØlH) RES OVF bit to 1.                                                                                                                                                           |

| 2           | INT2 (ICF)  | Interrupt signal set immediately when the the FRC data is latched into the ICR on the state transition of the barcode (BCRD) or external cassette (EAR) signal. This interrupt does not occur when latching is inhibited. This bit is reset by reading ICRH.B (at PØ3H). |

| 1           | INT1 (ART)  | Interrupt signal set when the ART RXRDY signal is set to 1. Reset by reading ARTDIR (P14H).                                                                                                                                                                              |

| 0           | INTO (7508) | Interrupt signal generated by the 7508 slave CPU.Reset by giving a response to the 7508.                                                                                                                                                                                 |

## Explanation:

INT4 through INT0 can be read even if the corresponding interrupts are masked off. INT0 is given the highest priority and INT4 the lowest priority.

Programming note: The PINE OS uses 7508, ART, and OVF interrupts.

#### 2.2.9 PØ4H: IER (Interrupt Enable Register) (write mode)

| Bit         | Name  | Description                                         |

|-------------|-------|-----------------------------------------------------|

| 7<br>6<br>5 |       | } / Ignored                                         |

| 4           | IER 4 | INT4 (EXT) interrupt status.  1:Enable 0:Disable    |

| 3           | IER 3 | INT3 (OVF) interrupt status.  1:Enable 0:Disable    |

| 2           | IER 2 | INT2 (ICF) interrupt status.  1: Enable 0: Disable  |

| 1           | IER 1 | INT1 (ART) interrupt status.  1:Enable 0:Disable    |

| 0           | IER O | INTØ (7508) interrupt status.<br>1:Enable 0:Disable |

#### Explanation:

The IER bits indicate the interrupt status of the corresponding interrupts.

#### Programming note:

The PINE OS stores the write data to the IER in system RAM area RZIER (ØF53EH) for use during update processing. When writing the IER directly from a user program, therefore, it is necessary to rewrite the contents of the RZIER simultaneously. The bit format of the RZIER is identical to that of the IER.

## Example: Enabling EXT interrupts

DI

LD A, (RZIER) RZIER: (ØF53EH)

OR 1ØH IER: (Ø4H)

LD (RZIER),A

OUT (IER),A

The PINE OS turns on and off the interrupt mask using BIOS MASKI.

In the normal state, 7508 and OVF interrupts are enabled and ART interrupt is enabled when the BIOS RSIOX open function is executed and disabled when the BIOS RSIOX close function is executed. ICF and EXT interrupts are disabled.

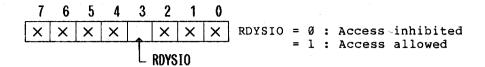

# 2.2.10 P05H: STR (Status Register) (read mode)

| Bit | Name   | Description                                                                                                                         |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| 7   | BANK 3 |                                                                                                                                     |

| 6   | BANK 2 |                                                                                                                                     |

| 5   | BANK 1 |                                                                                                                                     |

| 4   | BANK O |                                                                                                                                     |

| 3   | RDYSIO | Controls the serial bus used to interface to the 7508 slave CPU.  =1: Enables access to the 7508.  =0: Disables access to the 7508. |

| 2   | RDY    | RDY signal from the 7508.<br>Normally not used.                                                                                     |

| 1   | BCRD   | Data input from the barcode reader.                                                                                                 |

| 0   | EAR    | Data input from the external cassette.                                                                                              |

Explanation: See Section 1.2, "Address Map" for the values of BANK3 through BANK0.

### 2.2.11 PØ5H: BANKR (Bank Register) (write mode)

| Bit | Name   | Description                                                                                                                                        |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | BANK 3 |                                                                                                                                                    |

| 6   | BANK 2 | Main Memory Bank Register                                                                                                                          |

| 5   | BANK 1 |                                                                                                                                                    |

| 4   | BANK O | 7)                                                                                                                                                 |

| 3   | EDU    | Development board enable signal.  1: Uses the RAM on the development board.  0: Does not use the RAM on the development board.  Normally set to 0. |

| 2   | ECA    | RAM select signal for the development board. Normally set to $\emptyset$ .                                                                         |

| 1   | CKSW 1 | Clock Switch                                                                                                                                       |

| 0   | CKSW 0 | Oloch Owitch                                                                                                                                       |

Explanation:

See Section 1.2, "Address Map" for the values of BANK3 through BANK0.

Programming note:

The PINE OS stores the write data to the BANKR in system RAM area RZBANKR (ØF53DH) for use during update processing. When writing the BANKR directly from a user program, therefore, it is necessary to rewrite the contents of the RZBANKR simultaneously. The bit format of the RZBANKR is identical to that of the BANKR.

#### Clock Switch

| CKSW1 | CKSWO | System clock |

|-------|-------|--------------|

| 1     | 0     | 3. 6864 MHZ  |

| 1     | 1     | 3.072 MHZ    |

| 0     | *     | 3. 4576 MHZ  |

\* : Ignored

Note: For the PINE, CKSWl must be set to 1 and CKSW0 to 0 because the PINE uses the 3.6864 MHz system clock. Setting these bits to other values may cause serial I/F or timer malfunctions.

The PINE OS provides LOADX, STORX, LDIRX, JUMPX, and CALLX as BIOS functions for controlling the banks. For details of these routines, see 4.4, "Bank Switching" in Part II.

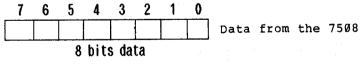

2.2.12 P06H: SIOR (Serial I/O Register) (read/write mode)

| Bit | Name  | Description        |

|-----|-------|--------------------|

| 7   | SIO 7 |                    |

| 6   | SIO 6 | 7                  |

| 5   | SIO 5 |                    |

| 4   | SIO 4 | 7508 data register |

| 3   | SIO 3 | 7500 data legister |

| 2   | SIO 2 |                    |

| 1   | SIO 1 |                    |

| 0   | SIO 0 |                    |

Explanation:

P06H holds 8-bit data received from the 7508 in the read mode and 8-bit data to be sent to the 7508 in the write mode.

# 2.2.13 PØ8H: VADR (VRAM Start Address Register) (write mode)

| Bit         | Name | Description         |

|-------------|------|---------------------|

| 7           | A15  |                     |

| 6           | A14  |                     |

| 5           | A13  | V-RAM Start Address |

| 4           | A12  |                     |

| 3           | A11  | <b>[</b> ]          |

| 2<br>1<br>0 |      | } Ignored           |

#### Explanation:

#### Programming note:

The PINE OS allocates addresses 0D800H through 0DFFFH for the system screen VRAM (VRAM2) and addresses 0E000H through 0E7FFH for the user screen VRAM (VRAM1).

The address of the currently active VRAM is stored in LSCRVRAM (ØF294H). The VADR is loaded with the address data from LSCRVRAM + 1 (F295H).

#### 2.2.14 PØ9H: YOFF (Y Offset Register) (write mode)

| Bit | Name       | Description                        |  |  |

|-----|------------|------------------------------------|--|--|

| 7   | DSP        | Turns on and off LCD display.      |  |  |

|     |            | =1: Turns on display.              |  |  |

|     |            | =0: Turns off display.             |  |  |

| 6   |            | Ignored                            |  |  |

| 5   | <b>Y</b> 5 |                                    |  |  |

| 4   | Y4         | 7                                  |  |  |

| 3   | <b>Y</b> 3 |                                    |  |  |

| 2   | <b>Y</b> 2 | Y-direction offset register (YOFF) |  |  |

| 1   | Y1         |                                    |  |  |

| 0   | γ0         | 7)                                 |  |  |

#### Explanation:

The YOFF defines the correspondence between the VRAM and the LCD panel. It gives the offset with respect to the top of the VRAM at which display is to start. When display reaches the bottom of the VRAM, it wraps around to the top of the VRAM. One screenful of display ends at (YOFF - 1)th dot line.

#### Programming note:

The PINE OS uses the YOFF for vertical scrolling. The current value of the YOFF is saved in LVRAMYOFF (@F2A@H).

#### 2.2.15 PØAH: FR (Frame Register) (write mode)

| Bit              | Name                     | Description    |

|------------------|--------------------------|----------------|

| 7<br>6<br>5<br>4 |                          | ] Ignored      |

| 3<br>2<br>1<br>0 | FR3<br>FR2<br>FR1<br>FR0 | Frame Register |

Explanation:

The FR defines the LCD frame frequency. The table below shows the relationship between the frame register and frame frequencies.

| FR  |     |     | LCD frame frequency (in Hz) |         |         |          |

|-----|-----|-----|-----------------------------|---------|---------|----------|

| FR3 | FR2 | FR1 | FR0                         | 3.68MHz | 3.07MHz | 2. 45MHz |

| 0   | 1   | 0   | 0                           | 106     | 88      | 70       |

| 0   | 1   | 0   | 1                           | 86      | 72      | 57       |

| 0   | 1   | 1   | 0                           | 72      | 60      | 48       |

| 0   | 1   | 1   | 1                           | 62      | 52      | 41       |

| 1   | 0   | 0   | 0                           | 55      | 46      | 36       |

| 1   | 0   | 0   | 1                           | 49      | 41      | 32       |

| 1   | 0   | 1   | 0                           | 44      | 37      | 29       |

| 1   | 0   | 1   | 1                           | 40      | 33      | Invalid  |

| 1   | 1   | 0   | 0                           | 37      | Invalid | Invalid  |

| 1   | 1   | 0   | 1                           | 34      | Invalid | Invalid  |

FR values (0000) through (0011), (1110), and (1111) are invalid.

Programming note:

The 3.68 MHz column in the table applies to the PINE since its system clock is 3.6864 MHz. The PINE OS loads the FR with 06H when executing the power-on, reset, and system initialize functions.

#### 2.2.16 PØBH: SPUR (SpeedUp Register) (write mode)

| Bit | Name  | Description     |  |

|-----|-------|-----------------|--|

| 7   |       | Ignored         |  |

| 6   | PRE2  |                 |  |

| 5   | PRE1  | } Define TPRE.  |  |

| 4   | PRE0  | ] }             |  |

| 3   |       | Ignored         |  |

| 2   | POST2 |                 |  |

| 1   | POST1 | } Define TPOST. |  |

| 0   | POSTO |                 |  |

#### Explanation:

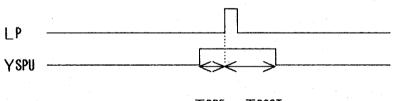

The SPUR defines the timing at which the impedance of the power supply to the LCD is to be reduced to suppress the voltage fluctuations occurring (due to increased current) during the rewrite of LCD panel data.

TPRE and TPOST define the pulse width of the YSPU which is used to save the power to the LCD unit. TPRE specifies the time interval before the LP signal and TPOST the delay time after LP. LP an LCD control signal and gives the latch pulse to the LCD shift register.

TPRE TPOST

The table below lists the TPRE and TPOST values for the frame frequency of 50. The actual time values can be obtained from: 50

TPRE (TPOST) = ----- x (Value taken from table)

Frame frequency

| PRE2 | PRE1 | PREO | TPRE (µs) |

|------|------|------|-----------|

| 0    | 0    | 0    | 77        |

| 0    | 0    | 1    | 67        |

| 0    | 1    | 0    | 57        |

| 0    | 1    | 1    | 48        |

| 1    | 0    | 0    | 38        |

| 1    | 0    | 1    | 28        |

| 1    | 1    | 0    | 18        |

| 1    | 1    | 1    | 9. 2      |

| POST2 | POST1 | POSTO | T POST (μs) |

|-------|-------|-------|-------------|

| 0     | 0     | 0     | 0.2         |

| 0     | 0     | 1     | 9.9         |

| 0     | 1     | 0     | 19          |

| 0     | 1     | 1     | 29          |

| 1     | 0     | 0     | 39          |

| 1     | 0     | 1     | 48          |

| 1     | 1     | 0     | 58          |

| 1     | 1     | 1     | 68          |

Programming note:

The PINE OS loads the SPUR with 43H when executing the power-on, reset, and system initialize functions.

#### 2.2.17 P1ØH - P13H

#### Explanation

PlØH through Pl3H are reserved for the cartridge interface. Their assignments differ depending on the cartridge mode (HS, DB, IO, or OT mode). See Section 4.1, "Cartridge Interface" for details about PlØH through Pl3H.

#### 2.2.18 P14H: ARTDIR (ART Data Input Register) (read mode)

| Bit Name |     | Description   |

|----------|-----|---------------|

| 7        | RD7 |               |

| 6        | RD6 |               |

| 5        | RD5 |               |

| 4        | RD4 | Receive data. |

| 3        | RD3 | Receive data. |

| 2        | RD2 |               |

| 1        | RD1 |               |

| 0        | RD0 | 7).           |

#### Explanation:

Pl4H is loaded with the parallel data converted from the serial data received over the RxD line. Bit 7 (RD7) is set to 0 when the 7-bit data format is used.

#### Programming note:

In PINE OS, serial data reception is conducted by an interrupt processing routine and the transfer of received data to the application program is done by a BIOS RSIOX function.

#### 2.2.19 P14H: ARTDOR (ART Data Output Register) (write mode)

| Bit | Name | Description |          |  |

|-----|------|-------------|----------|--|

| 7   | TD7  |             |          |  |

| 6   | TD6  | 1           |          |  |

| 5   | TD5  |             |          |  |

| 4   | TD4  | Send data.  |          |  |

| 3   | TD3  | Della data. | <i>C</i> |  |

| 2   | TD2  |             |          |  |

| 1   | TD1  |             |          |  |

| 0   | TDO  | ]           |          |  |

#### Explanation:

Pl4H is loaded with the parallel data to be sent over the serial TxD line. Bit 7 (TD7) is ignored when the 7-bit data format is used.

#### Programming note:

In PINE OS, serial data transmission and interface to the application program are conducted by BIOS RSIOX functions.

# 2.2.20 Pl5H: ARTSR (ART Status Register) (read mode)

|     |          | The state of the s |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7   | RDSR     | Data Set Ready signal. Set to 1 when the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |          | RS-232C interface DSR terminal is set active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6   |          | Always set to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5   | FE       | Set to 1 to indicate a framing error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4   | OE       | Set to 1 to indicate an overrun error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3   | PE       | Set to 1 to indicate a parity error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2   | Tx Empty | Indicates that no data is present in the transmitter block. This bit is set when the ARTDOR transmit buffer and the parallel-to-serial converter are both empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1   | Rx RDY   | When set to 1, generates an INT1 (ART) interrupt request to the Z-80 CPU to indicate that a data byte is received from the serial communication line.  RxRDY is reset by reading the ARTDIR receive buffer (P14H). This bit may also be reset by the reset input or error reset command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0   | Tx RDY   | Set to 1 when the ARTDOR output buffer is emptied and reset when the buffer is loaded with send data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <pre>Explanation: FE (bit 5):</pre> | The receive data processing is not affected when a framing error condition occurs. The PINE continues to receive the next data byte and checks it against the framing error condition. If the stop bits are received normally, the PINE resets the FE bit.              |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OE (bit 4):                         | The receive data processing continues even when an overrun error occurs. The OE, however, is not reset when the next data byte is received                                                                                                                              |

| PE (bit 3):                         | normally. The OE bit can be reset only by issuing the error reset command (ER = 1) or reset signal. The resetting conditions for the PE bit are identical to those for the FE bit. Parity is checked only when PEN is set to 1, that is, PE is held at Ø when PEN is Ø. |

#### 2.2.21 P15H: ARTMR (ART Mode Register) (write mode)

| Bit | Name | Description                              |  |  |  |

|-----|------|------------------------------------------|--|--|--|

| 7   | STOP | Specifies the number of stop bits.       |  |  |  |

|     |      | =1: 2bit                                 |  |  |  |

|     |      | =0: 1bit                                 |  |  |  |

| 6   |      | Ignored                                  |  |  |  |

| 5   | EVEN | Specifies the parity check mode          |  |  |  |

|     |      | (valid only when PEN is 1).              |  |  |  |

|     |      | =1 : Even parity                         |  |  |  |

|     |      | =0 : Odd parity                          |  |  |  |

| 4   | PEN  | Enables or disables parity checking.     |  |  |  |

|     |      | =1 : Enables parity checking.            |  |  |  |

|     |      | =0 : Disables parity checking.           |  |  |  |

| 3   |      | Ignored                                  |  |  |  |

| 2   | DATA | Specifies the length of the serial data. |  |  |  |

|     |      | =1:8bit                                  |  |  |  |

|     |      | =0:7bit                                  |  |  |  |

| 1 0 |      | } Ignored                                |  |  |  |

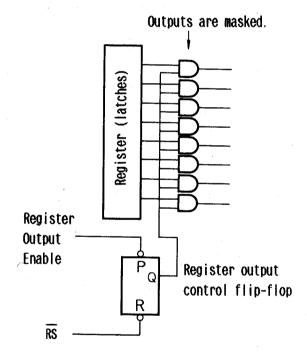

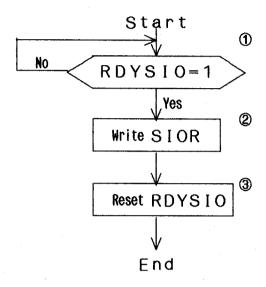

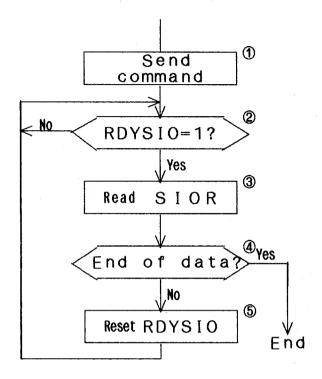

|     |      |                                          |  |  |  |